Toteuta vähävirtaisia mutta tehokkaita reunalaskentaratkaisuja Efinixin Quantum-FPGA-piireillä

Julkaisija DigiKeyn kirjoittajat Pohjois-Amerikassa

2020-03-17

Perinteisessä pilvilaskennassa esiintyy latenssiin, tietoturvaan, loppukäyttäjien yksityisyyden suojaan, käytettävissä olevaan kaistanleveyteen sekä yhteyksien luotettavuuteen liittyviä ongelmia. Niiden ratkaisemiseksi suunnittelijat ja järjestelmäarkkitehdit ovat siirtymässä kohti reunalaskentaa. Myös reunalaskenta sisältää omia haasteitaan kustannuksista, laitteiden koosta, suorituskyvystä ja virrankulutuksesta aina skaalautuvuuteen, joustavuuteen ja päivitettävyyteen. Tämä on erityisen totta silloin, kun pyritään tekemään enemmän kuvankäsittelyä ja toteuttamaan tekoäly- ja koneoppimisalgoritmeja lähempänä datan lähdettä.

Tämän tuloksena suunnittelijat ovat luopumassa perinteisistä mikrokontrollereista (MCU) tai sovellusprosessoreista (AP) ja valitsevat useammin uudelleenohjelmoitavia porttimatriiseja (FPGA), jotka kykenevät rinnakkaiseen prosessointiin. FPGA-piirien rakenne ja toteutustavat ovat kehittyneet tasaisesti, joten nykyisin ne voivat täyttää monia tai jopa kaikki näistä vaatimuksista joko itsenäisiä laitteina tai yhdessä MCU- ja AP-piirien kanssa. Monet suunnittelijat eivät kuitenkaan tunne FPGA-piirejä ja ovat huolissaan niiden korkeasta oppimiskynnyksestä.

Tässä artikkelissa kerrotaan lyhyesti siirtymisestä pilvilaskennasta reunalaskentaan sekä siitä, miksi perinteiset suoritinarkkitehtuurit eivät suoriudu yhtä hyvin kuvankäsittelystä, tekoälystä ja koneoppimisesta. Sen jälkeen tarjotaan lyhyt katsaus FPGA-piireihin ja siihen, miksi niiden arkkitehtuuri on edullinen dataintensiivisiä reunasovelluksia varten. Lopuksi esitellään uusi FPGA-tyyppi, Efinixin Quantum-teknologia, ja sen käyttötarkoitukset.

Mihin reunalaskentaa tarvitaan?

Perinteisessä pilvilaskennassa dataa kerätään monista etäsijainneista ja syötetään pilvipohjaiseen järjestelmään varastointia ja analysointia varten. Tässä lähestymistavassa on kuitenkin monia haittapuolia. Niihin kuuluvat suurten datamäärien siirtokustannukset, datan eheyden ja tietoturvan säilyttäminen siirron aikana, reagoinnin latenssit, loppukäyttäjän yksityisyyssuojan varmistaminen sekä usein epäluotettavat internetyhteydet ja käytettävissä olevan kaistan vajaa hyödyntäminen.

Nimensä mukaisesti reunalaskenta tarkoittaa, että prosessointi eli laskenta ja analysointi siirretään lähemmäs internetin reunaa, siihen pisteeseen jossa dataa generoidaan, analysoidaan, kerätään ja sovelletaan. Termi ei sinällään koske jotakin tiettyä sovellusta tai laitetta, ja suunnittelijat voivat halutessaan suorittaa kaiken laskennan pelkästään verkon reunalla tai hyödyntää tarpeen mukaan myös osittain pilven laskentatehoa.

Reunalaskentasovelluksia käytetään muun muassa älytehtaissa, älykaupungeissa, älykodeissa ja älykkäässä liikenteessä. Reunalaitteet voivat myös olla joko suuria ja tehokkaita palvelimia tai suhteellisen pieniä anturi- ja aktuaattorijärjestelmiä, jotka sijaitsevat aivan internetin reunalla, siis datan syntymispisteessä.

FPGA-piirien edut

Laskentamielessä perinteiset suorittimet ovat erittäin tehokkaita päätöksenteossa ja peräkkäisissä tehtävissä, mutta todella tehottomia monien datankäsittelyalgoritmien, kuten kuvankäsittelyn, tekoälyn ja koneoppimisen näkökulmasta. Nämä tehtävät voidaan usein peräkkäisyyden sijaan jakaa lukemattomiksi rinnakkaisiksi prosessointiketjuiksi. Juuri nämä sovellukset ovat siirtymässä verkon reunalle tai jopa tiedon alkupisteeseen.

Koska FPGA-piirit voidaan ohjelmoida (konfiguroida) toteuttamaan mikä tahansa toimintojen yhdistelmä, ne voivat suorittaa kuvankäsittely-, tekoäly- ja koneoppimisalgoritmeja massiivisesti rinnakkaistettuina, minimoiden näin latenssin ja vähentäen samalla tehonkulutusta. Ohjelmoitavan päärakenteen lisäksi FPGA-piireissä on mukana digitaalisia signaalinkäsittelylohkoja (DSP), joiden erikoiskertoimet nopeuttavat DSP:tä käyttäviä sovelluksia huomattavasti. FPGA-piirit sisältävät myös muistilohkoja, jotka helpottavat laskentaa suoraan piirillä ilman ulkoisen muistin käsittelyä.

Markkinoilla on useita FPGA-valmistajia, joilla kaikilla on oma mallitarjontansa. Yksi niistä, Efinix, on kehittänyt Quantumiksi kutsutun erityisen FPGA-arkkitehtuurin, joka soveltuu hyvin reunalaskentaan ja erityisesti kuvankäsittelyyn. Tämän teknologian ympärille se on kehittänyt Trion-FPGA-piirit (ja Quantum-ASIC-piirit), jotka tarjoavat perinteisiin FPGA-teknologioihin verrattuna nelinkertaisen suorituskykyedun tehonkulutukseen nähden (kuva 1). Integroitu kehitysympäristö Efinity toimii sekä FPGA- että ASIC-piirien kanssa.

Kuva 1: Hyvän teho-, suorituskyky- ja pinta-alasuhteensa ansiosta Trion-FPGA-piirit sopivat mukautetuksi logiikaksi, laskennan nopeuttamiseen, koneoppimiseen, syväoppimiseen sekä kuvankäsittelyyn. Efinity IDE:n avulla käyttäjät voivat siirtyä saumattomasti Trion-FPGA-piireistä Quantum-ASIC-piireihin erittäin suuria tuotantomääriä varten. (Kuvan lähde: Efinix)

Kuva 1: Hyvän teho-, suorituskyky- ja pinta-alasuhteensa ansiosta Trion-FPGA-piirit sopivat mukautetuksi logiikaksi, laskennan nopeuttamiseen, koneoppimiseen, syväoppimiseen sekä kuvankäsittelyyn. Efinity IDE:n avulla käyttäjät voivat siirtyä saumattomasti Trion-FPGA-piireistä Quantum-ASIC-piireihin erittäin suuria tuotantomääriä varten. (Kuvan lähde: Efinix)

Mitä Quantum-teknologia tarkoittaa?

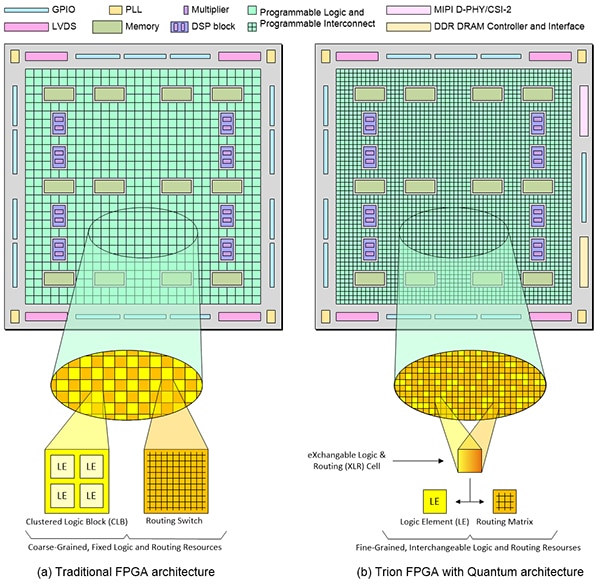

Perinteisten FPGA-piirien tavoin Trion-FPGA-piirit sisältävät muisti- ja DSP-lohkoja. Ero syntyy ohjelmoitavasta rakenteesta (kuva 2). Ohjelmoitavan logiikan ydin on logiikkaelementti (LE). Jokaisessa LE:ssä on hakutaulukko (LUT), multiplekseri ja rekisteri, jotka kaikki voidaan määrittää tarpeen mukaan. Perinteisten FPGA-piirien ohjelmoitavaa rakennetta voidaan kutsua karkeaksi.

Kuva 2: Perinteinen FPGA-arkkitehtuuri (a) on karkeaa, ja vaikka logiikka sekä yhteydet ovat ohjelmoitavia, ne ovat edelleen kiinteitä resursseja. Vertailun vuoksi Quantum-arkkitehtuuriin perustuvat Trion-FPGA-piirit (b) ovat hienojakoisia ja niiden logiikka- sekä reititysresurssit ovat vaihdettavissa. (Kuvan lähde: Max Maxfield)

Kuva 2: Perinteinen FPGA-arkkitehtuuri (a) on karkeaa, ja vaikka logiikka sekä yhteydet ovat ohjelmoitavia, ne ovat edelleen kiinteitä resursseja. Vertailun vuoksi Quantum-arkkitehtuuriin perustuvat Trion-FPGA-piirit (b) ovat hienojakoisia ja niiden logiikka- sekä reititysresurssit ovat vaihdettavissa. (Kuvan lähde: Max Maxfield)

Karkeissa rakenteissa useita LE:itä on kerätty yhteen suuremmiksi logiikkaklusterilohkoiksi (CLB). Jotkin toimittajat käyttävät niistä myös nimitystä logiikkaryhmälohko (LAB), mutta kyse on samasta asiasta.

On tärkeää huomata, että tämä kuva on abstraktio. Perinteisten FPGA-piirien CLB:t ja reitityskytkimet (ohjelmoitavat yhteydet) eivät oikeasti ole tällaisessa shakkiruudukkomaisessa rakenteessa. Ne ovat kuitenkin kiinteitä ja muuttamattomia sikäli, että ohjelmoitava logiikka on aina logiikkaa ja ohjelmoitavat yhteydet ovat aina yhteyksiä.

Perinteisiin arkkitehtuureihin verrattuna Trion-FPGA-piirit ovat paljon hienojakoisempia aina yksittäisen logiikkaelementin tasolle asti. Lisäksi jokainen logiikka- tai reitityssolu (XLR) voidaan määrittää toimimaan joko LE:nä tai reititysmatriisin osana.

Quantum-arkkitehtuurissa käytetyt konfiguraatiosolut ovat SRAM-pohjaisia, mikä tekee teknologiasta erittäin joustavaa. Ne voidaan valmistaa normaalilla CMOS-prosessilla, eikä prosessiin tarvita lisävaiheita, joita muiden keskihintaisten FPGA-piirien käyttämät flash-muistin kirjoitus- tai ohjausjärjestelyt vaativat.

Tämä ohjelmallisesti määritettävä logiikka ja reititys sekä tehokkaat, adaptiiviset yhteydet antavat Quantum-teknologiaan pohjautuville ratkaisuille nelinkertaisen edun tehon, suorituskyvyn ja pinta-alan suhteen verrattuna perinteisiin, samalla prosessiteknologialla toteutettuihin SRAM-pohjaisiin FPGA-piireihin.

Samoin Quantum-arkkitehtuurilla toteutetut FPGA-piirit vaativat vain seitsemän metallikerrosta perinteisten FPGA-piirien yli kahdentoista sijaan. Koska jokainen metallikerros vaatii useita maskaus- ja prosessointivaiheita, vain seitsemää kerrosta käyttämällä vähennetään suunnittelu- ja valmistuskustannuksia sekä lisätään tuotantoa.

Kaikki nämä ominaisuudet ovat erittäin hyödyllisiä suunnittelijoille, jotka etsivät kustannus-, koko-, suorituskyky- ja joustavuushyötyjä reunalaskentaan ja kuvankäsittelyyn. Näin Trion-FPGA-piirit sopivat erinomaisesti sekä perinteisiin FPGA-sovelluksiin että jatkuvasti lisääntyviin reunalaskenta- ja kuvankäsittelysovelluksiin. Jälkimmäisestä esimerkkejä ovat mobiililaitteet, esineiden internet (IoT), automaatio, robotiikka, antureiden yhdistäminen, konenäkö, tekoäly ja koneoppiminen.

Trion-FPGA-piirien rakenne

Trion-FPGA-piirit valmistetaan 40 nanometrin (nm) matalan tehon prosessilla, ja niiden logiikkaelementtien määrä vaihtelee neljäntuhannen ja kahdensadan tuhannen välillä, vaikka prosessi skaalautuukin tarvittaessa myös paljon suurempiin laitteisiin. Kaikissa Trion-FPGA-piireissä on muisti- ja DSP-lohkoja, mutta niiden kapasiteetti ja lukumäärä vaihtelee laitteen koon mukaan. Pienemmät laitteet kuten T4F81C2 ovat minimalistisempia (ne sisältävät 3 888 LE:tä, 78 848 muistibittiä ja 59 GPIO:ta), ja ne on tarkoitettu kannettavien laitteiden ohjauslogiikan toimintoihin.

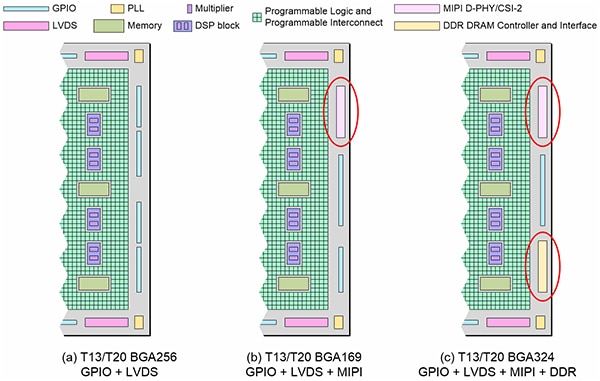

T20F256C3-piirin kaltaiset kehittyneemmät mallit sisältävät vastaavasti enemmän resursseja (19 728 LE:tä, 1 069 548 muistibittiä, 195 GPIO:ta). T13F256C3 vastaa piiriä T20F256C3, mutta sisältää 12 828 LE:tä. T13/T20:n tyyppisistä laitteista on myös eri versioita (kuva 3).

Kuva 3: Efinix T13/T20 BGA256 -piirit (a) ovat yleiskäyttöisiä FPGA-piirejä, jotka ovat hyvä valinta paljon vaadittaessa useita I/O-linjoja; T13/T20 BGA169 -piirit (b) sisältävät kaksi kiinteää MIPI D-PHY/CSI-2 -ydinlohkoa sovelluksiin, joissa tarvitaan MIPI-kamerarajapintaa; ja T13/T20 BGA324 -piirit (c) täydentävät MIPI-rajapintaa kiinteällä x16-bittisellä kaksinkertaisen datanopeuden (DDR) DRAM-rajapinnalla ja -ohjaimella käyttötarkoituksiin, joissa muistilta vaaditaan paljon kaistanleveyttä. (Kuvan lähde: Max Maxfield)

Kuva 3: Efinix T13/T20 BGA256 -piirit (a) ovat yleiskäyttöisiä FPGA-piirejä, jotka ovat hyvä valinta paljon vaadittaessa useita I/O-linjoja; T13/T20 BGA169 -piirit (b) sisältävät kaksi kiinteää MIPI D-PHY/CSI-2 -ydinlohkoa sovelluksiin, joissa tarvitaan MIPI-kamerarajapintaa; ja T13/T20 BGA324 -piirit (c) täydentävät MIPI-rajapintaa kiinteällä x16-bittisellä kaksinkertaisen datanopeuden (DDR) DRAM-rajapinnalla ja -ohjaimella käyttötarkoituksiin, joissa muistilta vaaditaan paljon kaistanleveyttä. (Kuvan lähde: Max Maxfield)

MIPI CSI-2 on mobiililaitteissa ja muilla markkinoilla yleisimmin käytetty kamerarajapinta, sillä se kuluttaa vähän tehoa ja tarjoaa alhaisen latenssin sekä edullisen piirien välisen yhteyden. Se tukee myös laajaa valikoimaa tehokkaita kuvaformaatteja, kuten 1080p-, 4K- ja 8K-videota (sekä tätäkin korkeampia videotarkkuuksia) sekä korkean tarkkuuden kuvia. Erityisen kiinnostavaa tässä yhteydessä on, että MIPI CSI-2 on suosituin rajapinta verkon reunan näköanturisovelluksissa. Näitä sovelluksia varten T13/T20 BGA169 -FPGA-piirit sisältävät kaksi kiinteää MIPI D-PHY/CSI-2 -ydinlohkoa (edelleen kuvassa 3).

DDR-muisti tukee nopeaa datan siirtoa, mutta se vaatii myös tiukan ajoitusprotokollan noudattamista. Vahvistettujen MIPI D-PHY/CSI-2 -rajapintojen lisäksi Trion T13/T20 BGA324 -piirit (kuva 3) sisältävät myös vahvistetun x16-bittisen DDR DRAM -rajapinnan ja ohjaimen sellaisia sovelluksia varten, jotka vaativat muistilta paljon kaistanleveyttä.

Quantum-ASIC-piirit

Kuten yllä mainittiin, Trion-FPGA-piirien konfiguraatiosolut ovat SRAM-pohjaisia. Tämän vuoksi Trion-FPGA-piireihin on ladattava konfiguraatiotiedot käynnistyksen yhteydessä joko ulkoiselta muistilaitteelta tai isäntäsuorittimen suorina muistikäskyinä. Jotta ratkaisua voidaan käyttää massatuotannossa, Efinix tarjoaa myös Quantum-kiihdytettyjä sulautettuja FPGA-ratkaisuja (eFPGA) Quantum-ASIC-piirien muodossa. Efinix voi tarjota T4-, T8-, T13- tai T20-piiriä käyttävän ratkaisun pohjalta maskilla ohjelmoituja Quantum ASIC -versioita, jotka käynnistyvät ilman ulkoista konfiguraatiolaitetta.

Suunnittelu ja kehitys Trion-FPGA-piireillä

Efinix tarjoaa useita erilaisia arviointialustoja ja kehityssarjoja, joilla käyttäjät voivat tutustua Trion-FPGA-piireihin. Näitä ovat muun muassa Trion T8F81C-DK -kehityssarja T8 Trion FPGA -piirille, Trion T20F256C-DK -arviointipiirilevy T20 Trion FPGA -piirille sekä Trion T20MIPI-DK -kehityssarja T20 MIPI D-PHY/CSI-2 -piirille.

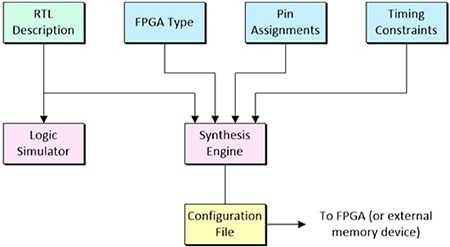

Eräs yleisimmistä FPGA-kehitykseen käytetyistä tekniikoista on LDD (language-driven design, kieliohjattu suunnittelu). Siihen kuuluu suunnittelutavoitteen kuvaaminen rekisterisiirtotasoksi (RTL) kuvatulla abstraktiotasolla käyttäen laitteistokuvauskieltä (HDL) ovat mm. Verilog ja VHDL. Kun tavoite on vahvistettu logiikkasimulaation kautta, tämä esitys syötetään synteesirutiinille, jolle kerrotaan myös FPGA-kohdepiirin tyyppi, pinnimääritykset sekä ajoitusta koskevat rajoitteet (esim. suurin tulon ja lähdön välinen viive. Synteesirutiini tuottaa konfiguraatiotiedoston, joka ladataan joko suoraan FPGA-piiriin tai SRAM-pohjaisissa piireissä ulkoiseen muistilaitteeseen (kuva 4).

Kuva 4: Logiikkasimulaation avulla tehdyn vahvistuksen jälkeen RTL-suunnittelukuvaus syötetään synteesirutiinille, jolle kerrotaan myös FPGA-kohdepiirin tyyppi, pinnimääritykset sekä ajoitusta koskevat rajoitteet. Synteesirutiini tuottaa konfiguraatiotiedoston, joka ladataan FPGA-piiriin. (Kuvan lähde: Max Maxfield)

Kuva 4: Logiikkasimulaation avulla tehdyn vahvistuksen jälkeen RTL-suunnittelukuvaus syötetään synteesirutiinille, jolle kerrotaan myös FPGA-kohdepiirin tyyppi, pinnimääritykset sekä ajoitusta koskevat rajoitteet. Synteesirutiini tuottaa konfiguraatiotiedoston, joka ladataan FPGA-piiriin. (Kuvan lähde: Max Maxfield)

Efinixin Efinity IDE on tämäntyyppinen työkalu. Tämä ohjelmisto tarjoaa täyden työnkulun RTL:stä bittivirraksi sekä yksinkertaisen graafisen käyttöliittymän ja tuen komentoriviltä syötetyille komentosarjoille. Intuitiivinen ohjausnäkymä opastaa kehittäjää työnkulussa (synteesi, asettelu, reititys, bittivirran generointi), ja jokaista vaihetta voidaan ohjata automaattisesti tai manuaalisesti. Kehittäjät voivat hyödyntää Efinityn synteesirutiinia hyödyntääkseen täysimittaisesti Trion-FPGA-piirien Quantum-arkkitehtuuria, jolloin voidaan luoda laitteita, jotka tarjoavat nelinkertaisen edun tehon, suorituskyvyn ja pinta-alan suhteen.

Paitsi, että Efinity IDE tukee kaupallisen ModelSim- ja NCSim- sekä ilmaisen IVerilog-simulaattorin simulointityönkulkuja, se sisältää myös Interface Designer -toiminnon, jolla voidaan rajoittaa logiikkaa ja määrittää pinnejä laitteen reunoilla sijaitseville lohkoille, Floorplan Editor -toiminnon, jolla voidaan selata suunnitelman logiikka- ja reitityselementtien sijoittelua, Timing Browser -ajoitusselaimen ja staattisen aika-analyysin, joilla voidaan mitata laitteen suorituskykyä, sekä integroidun laitteiston vianetsintätoiminnon, logiikka-analysaattorin ja virtuaalisia I/O-vianetsintäytimiä.

Yhteenveto

Suunnittelijoiden siirtäessä yhä enemmän kuvankäsittelyä ja tekoälyyn sekä koneoppimiseen liittyvää laskentaa verkon reunalle joko pilvilaskennan sijaan tai sen tukemiseksi heidän tulee harkita FPGA-piirien käyttöä laskenta-arkkitehtuurissaan parempana ratkaisuna kustannuksiin, suorituskykyyn, tehonkulutukseen, kokoon, skaalautuvuuteen, joustavuuteen ja päivitettävyyteen liittyviin ongelmiin.

Osa suunnittelijoista saattaa kokea oppimisen haastavana, mutta Efinixin Quantum-teknologian kaltaisten edistysaskeleiden ansiosta investointi saattaa maksaa itsensä takaisin nopeastikin alentuneiden kustannusten, pienemmän koon, korkeamman suorituskyvyn ja paremman joustavuuden kautta.

Näin FPGA-piirit sopivat nyt ihanteellisesti sekä perinteisiin FPGA-sovelluksiin että lisääntyvään reunalaskentaan mobiilisovellusten, IoT:n, automaation, robotiikan, anturifuusion, konenäön, tekoälyn ja koneoppimisen saralla.

Lisäresurssit

- Perusteet: IoT, IIoT, AIoT ja miksi ne ovat teollisuusautomaation tulevaisuus

- FPGA-piirien perusteet: Mitä FPGA-piirit ovat ja miksi niitä tarvitaan?

- FPGA-piirien perusteet – Osa 2: Alkuun Lattice Semiconductorin FPGA-piireillä

- FPGA-piirien perusteet – Osa 3: Alkuun Microchip Technologyn FPGA-piireillä

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.