Miksi ja miten käyttää Efinixin FPGA-piirejä AI- ja ML-pohjaiseen kuvantamiseen – Osa 1: Aloitusopas

Julkaisija DigiKey's European Editors

2023-04-20

Toimittajan huomautus: FPGA-arkkitehtuurien uudet menetelmät mahdollistavat hienojakoisemman ohjauksen ja paremman joustavuuden koneoppimisen (Machine Learning, ML) ja tekoälyn (Artificial Intelligence, AI) tarpeiden täyttämiseksi. Tämän kaksiosaisen sarjan ensimmäisessä osassa tutustutaan yhteen tällaiseen Efinixin arkkitehtuuriin ja siihen, miten aloittaa sen käyttö kehitysalustan avulla. Toisessa osassa käsitellään kehitysalustan yhdistämistä ulkoisiin oheislaitteisiin, kuten kameraan.

FPGA-piireillä on tärkeä rooli mitä erilaisemmissa sovelluksissa aina teollisesta ohjauksesta ja turvallisuudesta robotiikkaan, ilmailuun ja autoteollisuuteen. Ohjelmoitavan logiikkaytimen monipuolisuuden ja laajan yhdistettävyyden ansiosta yksi FPGA-piirien yleistyvistä käyttötapauksista ovat kuvankäsittelyn koneoppimissovellukset. FPGA-piirit sopivat ihanteellisesti ratkaisuihin, joissa on useita nopeita kamerarajapintoja. Lisäksi ne mahdollistavat tarkoitukseen varattujen prosessointiputkien implementoinnin logiikkaan ja näin ne poistavat CPU- ja GPU-ratkaisuihin liittyvät pullonkaulat.

Useissa sovelluksissa vaaditaan kuitenkin enemmän koneoppimis- ja tekoälytoimintoja sekä hienojakoisempaa ohjausta, reititystä ja logiikkaa, joihin konfiguroitaviin logiikkalohkoihin (Configurable Logic Block, CLB) pohjautuvat klassiset FPGA-arkkitehtuurit eivät kykene. Uudemmat FPGA-arkkitehtuurit ratkaisevat nämä ongelmat. Esimerkiksi Efinixin Quantum-arkkitehtuurissa hyödynnetään XLR (eXchangeable Logic and Routing) ‑lohkoja.

Tässä artikkelissa käsitellään Efinixin FPGA-arkkitehtuurin keskeisiä ominaisuuksia painottaen tekoäly- ja koneoppimista sekä esitellään tosimaailman toteutuksia. Sen jälkeen artikkelissa esitellään kehitysalusta ja työkaluja, joiden avulla kehittäjät pääsevät nopeasti alkuun seuraavan tekoäly-/koneoppimiskuvantamissovelluksensa suunnittelussa.

Efinixin FPGA-laitteet

Efinix tarjoaa tällä hetkellä kaksi laiteperhettä. Yritys lanseerasi ensin SMIC 40LL ‑prosessilla valmistetun Trion-tuoteperheen, joka tarjoaa logiikkatiheydet 4 000 (4K) – 120 000 (120K) logiikkaelementtiä (Logic Element, LE). Uusin huippusuositulla 16 nanometrin (nm) TSMC-prosessilla valmistettu Titanium-tuoteperhe tarjoaa logiikkatiheydet 35 000 (35K) – 1 000 000 (1M) logiikkaelementtiä.

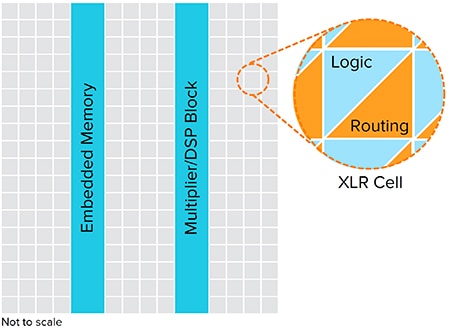

Kumpikin tuoteperhe pohjautuu FPGA-maailmassa ainutlaatuiseen Quantum-arkkitehtuuriin. Tavallinen FPGA-arkkitehtuuri perustuu CLB-lohkoihin, jotka yksinkertaistettuna sisältävät hakutaulukon (Look-Up Table, LUT) ja kiikkuja. CLB-lohkot suorittavat logiikkayhtälöitä, jotka yhdistetään reitityksen avulla. Efinixin Quantum-arkkitehtuurissa XLR-lohkot auttavat korvaamaan erilliset logiikka- ja reitityslohkot.

XLR-lohkon erikoisuus on mahdollisuus konfiguroida se toimimaan hakutaulukkopohjaisena logiikkalohkona, rekisterinä ja summaimena tai reititysmatriisina. Tämä menetelmä mahdollistaa hienojakoisemman arkkitehtuurin, joka tarjoaa monipuolisemman reitityksen ja mahdollistaa sekä logiikka- että reitityspainotteiset toteutukset toivotun suorituskyvyn saavuttamiseksi.

Kuva 1: XLR-lohkon erikoisuus on mahdollisuus konfiguroida se toimimaan hakutaulukkopohjaisena logiikkalohkona, rekisterinä ja summaimena tai reititysmatriisina. (Kuvan lähde: Efinix)

Kuva 1: XLR-lohkon erikoisuus on mahdollisuus konfiguroida se toimimaan hakutaulukkopohjaisena logiikkalohkona, rekisterinä ja summaimena tai reititysmatriisina. (Kuvan lähde: Efinix)

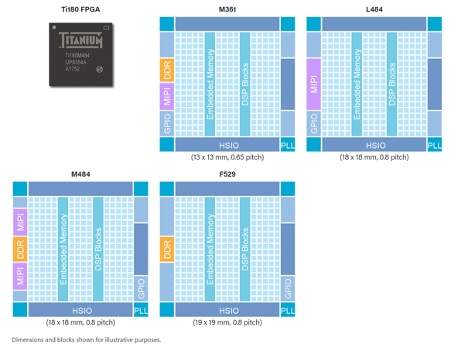

Uusimman Titanium-tuoteperheen laitteet tarjoavat kehittäjille edistyneimmät ominaisuudet (kuva 2). XLR-ytimen ohella niissä on usean gigabitin sarjalinkit, jotka toimivat laitteesta riippuen 16 tai 25,8 gigabitin sekuntinopeudella (Gbps). Nämä usean gigabitin linkit ovat erittäin tärkeitä nopean tiedonsiirron mahdollistamiseksi piirin sisällä ja sen ulkopuolella.

Kuva 2: Titanium Ti180 ‑FPGA on saatavilla eri versioina riippuen väyläleveys-, I/O- ja muistivaatimuksista. (Kuvan lähde: Efinix)

Kuva 2: Titanium Ti180 ‑FPGA on saatavilla eri versioina riippuen väyläleveys-, I/O- ja muistivaatimuksista. (Kuvan lähde: Efinix)

Titanium-laitteet tarjoavat myös paljon erilaisia tuloja ja lähtöjä (I/O), jotka voi ryhmitellä GPIO-linjoiksi ja jotka voivat tukea epäsymmetrisiä I/O-standardeja, kuten matalan jännitteen (3,3; 2,5 tai 1,8 voltin) CMOS (LVCMOS).

Titanium-laitteissa on nopeaa ja differentiaalimuotoista tiedonsiirtoa varten nopea I/O (High-Speed I/O, HSIO), joka tukee epäsymmetrisiä I/O-standardeja, kuten LVCMOS (1,2 ja 1,5 volttia) sekä SSTL ja HSTL. HSIO-tekniikan tukemiin differentiaalimuotoisiin I/O-standardeihin lukeutuvat LVDS (Low-Voltage Differential Signaling), differentiaalinen SSTL ja HSTL.

Modernit FPGA-piirit tarvitsevat myös lähelle sijoitetun korkean kaistanleveyden muistin, jota käytetään kuvankäsittelysovelluksissa kuvien ja signaalinkäsittelyn näytetietojen säilyttämiseen sekä FPGA-piirillä toteutetuilla prosessoreilla suoritettavien käyttöjärjestelmien ja ohjelmistojen suorittamiseen. Titanium-laitevalikoima on yhteensopiva DDR4-muistin sekä matalan virran DDR4(x)-muistin (LPDDR4(x)) kanssa. Valitusta Titanium-laitteesta riippuen tuettu väylän kaistanleveys on x32 (J) tai x16 (M). Jotkin laitteet eivät tue LPDDR4-muistia (L).

Titanium-FPGA-piirit ovat SRAM-pohjaisia, ja ne vaativat konfiguraatiomuistin. Laitteen konfigurointi suoritetaan joko master- tai slave-tilassa toimivan SPI- (Serial Peripheral Interconnect) tai JTAG-liitännän kautta. Konfiguraatiomenetelmän suojaamiseksi Titanium-FPGA käyttää bittivirran AES GCM ‑salausta sekä AES GCM- ja RSA-4096-menetelmiä bittivirran todentamiseen. Tämä vahva tietoturva on tarpeen, koska FPGA-piirejä käytetään reunasovelluksissa, joihin vihamieliset toimijat voivat saada helpommin pääsyn niiden toiminnan manipuloimiseksi.

Kehitysalustan esittely

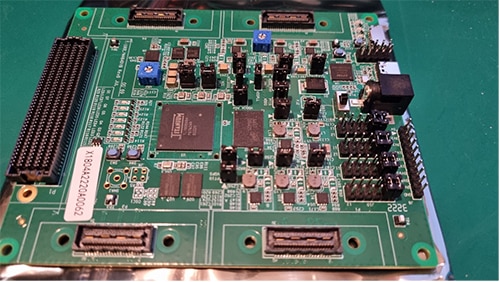

Kehitysalustat ovat kriittinen osa FPGA-arviointiprosessia, sillä niitä voi käyttää laitteen ominaisuuksiin tutustumiseen ja sovellusten prototyyppikehitykseen, mikä laskee kokonaisriskiä. Ensimmäinen saatavilla oleva kehitysalusta Titaniumin FPGA-piirien arviointiin ja sovellusten prototyyppikehitykseen on Ti180 M484 (kuva 3). Kortissa on FMC (FPGA Mezzanine Card) -liitin ja neljä Samtecin QSE-liitintä.

Kuva 3: Titanium-FPGA-piirin lisäksi Ti180 M484 ‑kehityssarjassa on FMC-liitin ja neljä Samtecin QSE-liitintä. (Kuvan lähde: Adam Taylor)

Kuva 3: Titanium-FPGA-piirin lisäksi Ti180 M484 ‑kehityssarjassa on FMC-liitin ja neljä Samtecin QSE-liitintä. (Kuvan lähde: Adam Taylor)

Tähän kehitysalustaan asennettu Ti180-FPGA sisältää 172 000 XLR-lohkoa, 32 globaalia kelloa, 640 digitaalista signaalinkäsittelyelementtiä (Digital Signal Processing, DSP) ja 13 megabittiä (Mbit) upotettua RAM-muistia. DSP-elementit mahdollistavat kiinteän pilkun 18 x 19 ‑kertolaskut ja 48-bittiset kertolaskut. Tämän DSP:n voi optimoida myös yhden komennon, usean arvon (Single Instruction, Multiple Data, SIMD) toimintaan kaksi- tai nelikanavaisella konfiguraatiolla. DSP-elementit voi myös määrittää suorittamaan liukulukutoimintoja.

Kuten useimmat kehitysalustat, myös Ti180 tarjoaa yksinkertaiset ledivalot ja painikkeet. Sen todellinen teho piilee kuitenkin sen rajapintaominaisuuksissa. Ti180-kehitysalustassa on nastamäärältään pieni FMC-liitin, joka mahdollistaa mitä erilaisimpien oheislaitteiden yhdistämisen. Koska FMC on laajalti käytetty standardi, saatavilla on useita FMC-kortteja, jotka mahdollistavat nopeiden analogi-digitaalimuuntimien (Analog-to-Digital Converter, ADC), digitaali-analogiamuuntimien (Digital-to-Analog Converter, DAC), verkkolaitteiden ja muisti-/tallennusratkaisujen liittämisen.

FMC-liitännän lisäksi kortissa on neljä Samtecin QSE-liitäntää, joihin kehittäjät voivat liittää laajennuskortteja. Näitä QSE-liittimiä käytetään MIPI-tuloihin ja -lähtöihin niin, että kukin QSE-liitin tarjoaa yhden MIPI-tulon tai -lähdön.

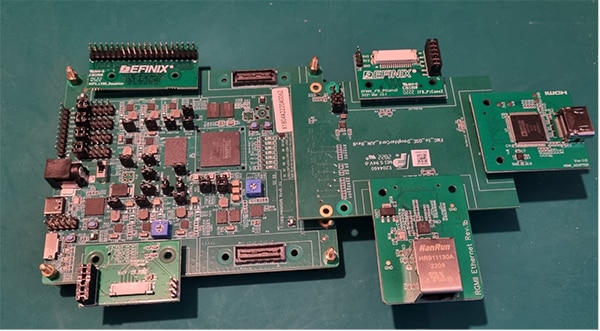

Kuva 4: Ti180 M484 ‑kehityssarja ja sen monipuoliset laajennusvaihtoehdot QSE- ja FMC-liitännöillä. (Kuvan lähde: Adam Taylor)

Kuva 4: Ti180 M484 ‑kehityssarja ja sen monipuoliset laajennusvaihtoehdot QSE- ja FMC-liitännöillä. (Kuvan lähde: Adam Taylor)

Ti180-kortissa on myös 256 megabittiä LPDDR4-muistia, koska kuvan- ja signaalinkäsittelysovelluksissa vaaditaan erittäin suorituskykyistä muistia. Lisäksi kehitysalusta tarjoaa laajan kellotaajuusvalikoiman (25; 33,33; 50 ja 74,25 megahertsiä), jota voi käyttää vaihelukitun silmukan (Phase Lock Loop, PLL) kanssa erilaisten sisäisten taajuuksien generoimiseen.

Reaaliaikainen ohjelmointi ja virheenkorjaus suoraan kortilla on kriittisen tärkeä ominaisuus, joka vaatii JTAG-liitännän. Tässä tuotteessa se toimii integroidun USB-C-liitännän kautta. Piirilevyllä on myös haihtumatonta muistia kahden 256 megabitin NOR Flash ‑muistipiirin muodossa. Niitä voidaan käyttää konfiguraatioratkaisun demonstrointiin.

Kortin virtalähteenä toimii sarjan mukana toimitettava universaali 12 voltin adapteri. Sarjan mukana toimitetaan myös kytkentäkortti FMC-muodosta QSE-muotoon sekä QSE-pohjaiset HDMI-, Ethernet-, MIPI- ja LVDS-laajennuskortit. Lisäksi Ti180-sarjan kuvankäsittelyominaisuuksien esittelemiseksi mukana on kaksikanavainen RPI-tytärkortti ja kaksi IMX477-kamerakorttia.

Ohjelmistoympäristö

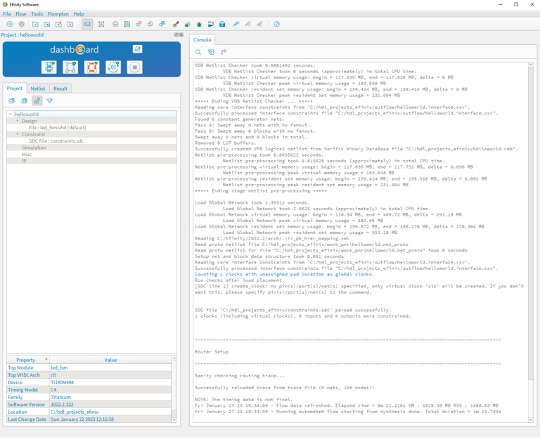

Ti180-kehitysalustalle tarkoitettujen sovellusten toteutukseen käytetään Efinixin Efinity-ohjelmistoa. Ohjelmisto mahdollistaa bittivirran generoimisen synteesillä sekä sijoitus ja reititys ‑menetelmällä. Se tarjoaa kehittäjille myös immateriaalioikeuslohkot (Intellectual Property block, IP block), ajoitusanalyysin ja piirin sisäisen virheenkorjauksen.

Huomaa, että Efinity-ohjelmiston käyttämiseen tarvitaan kehitysalusta. Mutta toisin kuin muiden toimittajien kohdalla, työkalusta ei ole erilliset lisenssit vaativia eri versioita.

Uudet projektit luodaan Efinityssä valitulle laitteelle. Tämän jälkeen projektiin voidaan lisätä RTL-tiedostoja ja luoda rajoitteet ajoitusta ja I/O-ratkaisua varten. Efinityssä luodaan myös I/O-ratkaisu hyödyntämällä HSIO-, GPIO- ja erityis-I/O-linjoja.

Kuva 5: Uudet projektit luodaan Efinityssä valitulle laitteelle. (Kuvan lähde: Adam Taylor)

Kuva 5: Uudet projektit luodaan Efinityssä valitulle laitteelle. (Kuvan lähde: Adam Taylor)

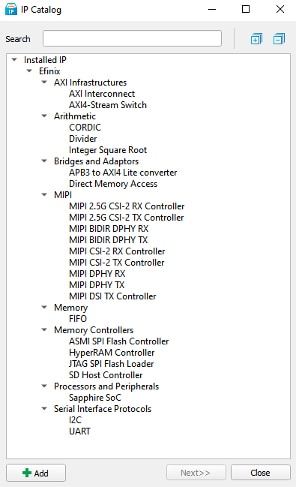

FPGA-suunnittelun kriittinen elementti on IP-lohkojen hyödyntäminen, erityisesti monimutkaisien IP-lohkojen, kuten AXI-yhteydet, muistiohjaimet ja ohjelmalliset mikroprosessorit eli niin kutsutut softcoret. Efinity tarjoaa kehittäjille runsaan valikoiman IP-lohkoja, joilla voidaan nopeuttaa suunnitteluprosessia.

Kuva 6: Efinity tarjoaa kehittäjille valikoiman IP-lohkoja suunnitteluprosessin nopeuttamiseksi. (Kuvan lähde: Adam Taylor)

Kuva 6: Efinity tarjoaa kehittäjille valikoiman IP-lohkoja suunnitteluprosessin nopeuttamiseksi. (Kuvan lähde: Adam Taylor)

FPGA-piirit ovat erinomaisia rinnakkaiskäsittelyrakenteiden toteuttamisessa, mutta monissa FPGA-sovelluksissa hyödynnetään myös ohjelmallisia mikroprosessoreita. Ne mahdollistavat peräkkäiskäsittelyn toteuttamisen esimerkiksi verkkotiedonsiirtoa varten. Ohjelmallisten mikroprosessoreiden toteuttamiseksi Efinix-laitteilla Efinity-ohjelmistossa on järjestelmäpiirien (System-on-Chip, SoC) Sapphire-konfigurointityökalu. Sapphiren avulla kehittäjä voi määritellä usean prosessorin järjestelmän, jossa on välimuistit, välimuistin yhtenäisyys eri prosessorien välillä sekä mahdollisuus suorittaa upotettua Linux-käyttöjärjestelmää. Kehittäjä voi valita Sapphiressa yhden ja neljän ohjelmallisen mikroprosessorin välillä.

Käytettävä ohjelmallinen mikroprosessori on RISC-V-käskykanta-arkkitehtuuriin pohjautuva VexRiscV. VexRiscV-prosessori on 32-bittinen toteutus, jossa on laajennukset liukuhihnoja varten sekä konfiguroitavat ominaisuudet, mikä tekee siitä ihanteellisen vaihtoehdon Efinix-laitteille. Valinnaisiin konfiguraatioihin sisältyvät kertoja, atomiset käskyt, liukulukulaajennukset ja pakatut käskyt. Järjestelmäpiirin kokoonpanosta riippuen suorituskyky vaihtelee välillä 0,86–1,05 DMIPS/MHz.

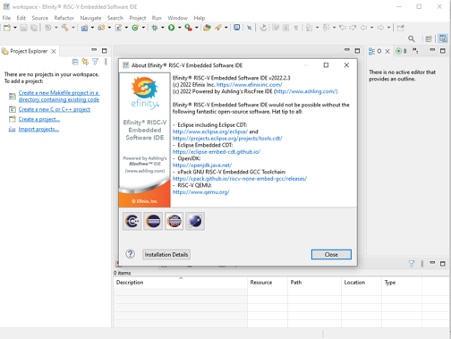

Kun laitteistoympäristö on suunniteltu ja implementoitu Efinix-laitteella, ohjelmasovellus voidaan kehittää Ashling RiscFree ‑ohjelmointiympäristössä. Ashling RiscFree on Eclipse-pohjainen ohjelmointiympäristö, joka mahdollistaa ohjelmasovellusten luomisen ja kääntämisen sekä virheenkorjauksen kohdelaitteella sovelluksen hienosäätämiseksi ennen käyttöönottoa.

Kuva 7: Ashling RiscFree on Eclipse-pohjainen ohjelmointiympäristö, joka mahdollistaa ohjelmasovellusten luomisen ja kääntämisen sekä virheenkorjauksen kohdelaitteella. (Kuvan lähde: Adam Taylor)

Kuva 7: Ashling RiscFree on Eclipse-pohjainen ohjelmointiympäristö, joka mahdollistaa ohjelmasovellusten luomisen ja kääntämisen sekä virheenkorjauksen kohdelaitteella. (Kuvan lähde: Adam Taylor)

Upotetun Linux-ratkaisun kehittämiseksi Buildroot tarjoaa kaikki tarpeelliset käynnistyskomponentit, mukaan lukien ensimmäisen vaiheen käynnistyslataaja, OpenSBI, U-Boot ja Linux. Jos reaaliaikainen ratkaisu on tarpeen, voidaan käyttää FreeRTOS-käyttöjärjestelmää.

Tekoälytoteutus

Efinixin tekoälytoteutus pohjautuu ohjelmalliseen RISC-V-mikroprosessoriin. Se hyödyntää RISC-V-prosessorin tukemia mukautettuja käskyjä TensorFlow Lite ‑ratkaisujen kiihdyttämiseksi. RISC-V-prosessorin ansiosta käyttäjät voivat luoda omia käskyjään, joita voidaan käyttää osana tekoälypäättelyyn liittyvää esi- ja jälkikäsittelyä. Tämä mahdollistaa responsiivisemmat ja deterministisemmat ratkaisut.

Hyvä ensimmäinen vaihe tekoälytoteutuksen kehityksessä on tutustua Efinixin mallikirjastoon, johon sisältyy tälle teknologialle optimoituja tekoäly- ja koneoppimismalleja. Efinix-laitteiden parissa työskentelevät kehittäjät voivat hyödyntää mallikirjastoa ja kouluttaa tekoälyverkkoja käyttämällä Jupyter Notebook- tai Google Colab ‑alustaa. Kun verkko on koulutettu, sen voi muuntaa liukulukumallista kvantisoiduksi versioksi käyttämällä TensorFlow Lite -muunninta.

TensorFlow Lite ‑muunnoksen jälkeen voidaan käyttää Efinixin tinyML-kiihdytintä käyttöönottovalmiin RISC-V-ratkaisun luomiseen. Kehittäjä voi käyttää tinyML-generaattoria kiihdytintoteutuksen mukauttamiseen ja projektitiedostojen generointiin. Valitusta arkkitehtuurista ja mukautuksesta riippuen kiihdytys voi olla tällä menetelmällä 4–200-kertainen.

Yhteenveto

Efinix-laitteiden ainutlaatuinen XLR-arkkitehtuuri tarjoaa kehittäjille joustavan alustan. Työkaluketju mahdollistaa RTL-toteutusten ohella kompleksiset järjestelmäpiiriratkaisut, joissa hyödynnetään ohjelmallisia RISC-V-prosessoreja. Ohjelmallisen SoC-prosessorin päälle voidaan rakentaa tekoäly-/koneoppimisratkaisu, joka mahdollistaa ML-päättelyn.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.