Miksi ja miten käyttää Efinixin FPGA-piirejä AI- ja ML-pohjaiseen kuvantamiseen – Osa 2: Kuvien lukeminen ja käsittely

Julkaisija DigiKey's European Editors

2023-05-05

Toimittajan huomautus: FPGA-arkkitehtuurien uudet menetelmät mahdollistavat hienojakoisemman ohjauksen ja enemmän joustavuutta koneoppimisen (ML) ja tekoälyn (AI) tarpeisiin vastaamiseen. Tämän kaksiosaisen sarjan ensimmäisessä osassa tutustutaan yhteen tällaiseen Efinixin arkkitehtuuriin ja siihen, miten aloittaa sen käyttö kehitysalustan avulla. Tässä toisessa osassa käsitellään kehitysalustan yhdistämistä ulkoisiin oheislaitteisiin, kuten kameraan, ja sitä, miten kuvankäsittelyn pullonkaulat voidaan poistaa käyttämällä FPGA-piiriä.

FPGA-piireillä on tärkeä rooli mitä erilaisemmissa sovelluksissa aina teollisesta ohjauksesta ja turvallisuudesta robotiikkaan, ilmailuun ja autoteollisuuteen. Ohjelmoitavan logiikkaytimen monipuolisuuden ja laajan yhdistettävyyden ansiosta yksi FPGA-piirien yleistyvistä käyttötapauksista ovat kuvankäsittelyn koneoppimissovellukset (ML). Rinnakkaisen logiikkarakenteensa vuoksi FPGA-piirit sopivat ihanteellisesti ratkaisuihin, joissa on useita nopeita kamerarajapintoja. Lisäksi ne mahdollistavat tarkoitukseen varattujen prosessointiputkien käytön logiikassa ja näin ollen CPU- ja GPU-ratkaisuihin liittyvien jaettujen resurssien aiheuttamien pullonkaulojen poistamisen.

Tämä toinen katsaus Efinixin Titanium-FPGA-piireihin keskittyy referenssikuvankäsittelysovellukseen, joka toimitetaan Ti180 M484 ‑kehitysalustan mukana. Artikkelin tavoitteena on ymmärtää ratkaisun osatekijöitä ja tunnistaa, missä FPGA-tekniikka mahdollistaa pullonkaulojen poistamisen tai tarjoaa kehittäjille muita etuja.

Ti180 M484 ‑pohjainen referenssimalli

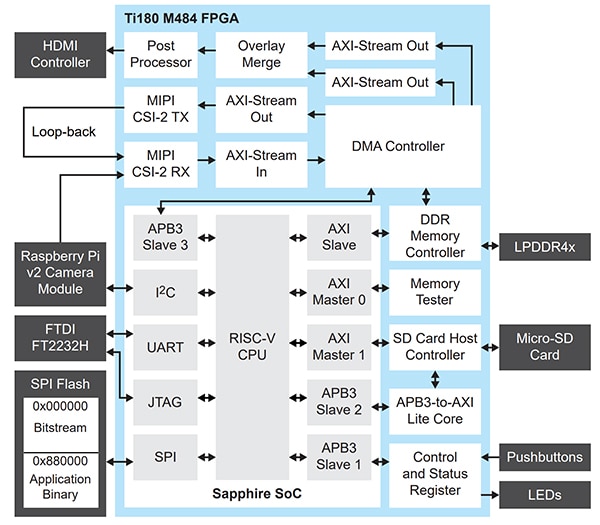

Referenssimalli (kuva 1) vastaanottaa kuvia useista MIPI-kameroista, käyttää LPDDR4x-muistia kehyspuskurina ja näyttää sitten kuvat HDMI-näytöllä. FPGA Mezzanine ‑kortti (FMC) ja kortin neljä Samtec QSE ‑liitäntää tarjoavat kameratulot ja HDMI-lähdön.

Kuva 1: Ti180 M484 ‑referenssimalli periaatteessa vastaanottaa kuvia useista MIPI-kameroista, käyttää LPDDR4x-muistia kehyspuskurina ja näyttää sitten kuvat HDMI-näytöllä. (Kuvan lähde: Efinix)

Kuva 1: Ti180 M484 ‑referenssimalli periaatteessa vastaanottaa kuvia useista MIPI-kameroista, käyttää LPDDR4x-muistia kehyspuskurina ja näyttää sitten kuvat HDMI-näytöllä. (Kuvan lähde: Efinix)

FMC–QSE-laajennuskorttia käytetään yhdessä HDMI-tytärkortin kanssa videolähtöä varten, kun taas kolmea QSE-liitintä käytetään DFRobot SEN0494 MIPI ‑kameroiden liittämiseen. Jos käytettävissä ei ole useita MIPI-kameroita, yhden ainoan kameran yksittäinen kamerakanava voidaan syöttää takaisin useampien kameroiden simuloimiseksi.

Yleisellä tasolla tämä sovellus saattaa vaikuttaa suoraviivaiselta. Useiden HD-MIPI-videovirtojen vastaanottaminen korkealla kuvataajuudella on kuitenkin haastavaa. Tässä tulevat esiin FPGA-teknologian hyödyt, sillä sen ansiosta voidaan hyödyntää useampia rinnakkaisia MIPI-virtoja.

Referenssimallin arkkitehtuuri hyödyntää sekä rinnakkaisia että peräkkäisiä käsittelymenetelmiä FPGA-piirissä. Kuvankäsittelyn toteuttamiseen käytetään rinnakkaisprosessointia, kun taas RISC-V-suoritin tarjoaa peräkkäiskäsittelyn, jota käytetään FPGA-hakutaulukoihin (LUT).

Kuvankäsittely voidaan monissa FPGA-pohjaisissa kuvankäsittelyjärjestelmissä jakaa kahteen elementtiin eli tulo- ja lähtövirtoihin. Tulovirta on yhdistetty kamera-/kennorajapintaan ja kennon lähtöön sovelletaan käsittelytoimintoja. Nämä toiminnot voivat sisältää Bayer-muunnoksen, valkotasapainon automaattisen korjauksen ja muita parannuksia. Lähtövirrassa kuva valmistellaan näyttöä varten. Tämä sisältää väriavaruuden muuttamisen (esim. RGB–YUV) ja jälkikäsittelyn haluttua lähtömuotoa, kuten HDMI:tä, varten.

Tulevan kuvan käsittelyketju toimii usein kennon pikselikellonopeudella. Tämä poikkeaa lähtöketjun ajoituksesta, jota käsitellään lähdön näyttötaajuudella.

Kehyspuskuria käytetään tulon yhdistämiseen lähtösignaalin käsittelyyn, ja se tallennetaan usein ulkoiseen korkean suorituskyvyn muistiin, kuten LPDDR4x. Tämä kehyspuskuri erottaa tulo- ja lähtökanavat toisistaan sallien pääsyn kehyspuskuriin oikosiirrolla sopivalla kellotaajuudella.

Ti180-referenssimallissa käytetään samankaltaista lähestymistapaa kuin edellä kuvatuissa konsepteissa. Tulevan kuvan käsittelyyn käytetään MIPI Camera Serial Interface 2 (CSI-2) ‑vastaanotinta, jossa on IP (Intellectual Property) -ydin, joka puolestaan käyttää Titanium FPGA -piirin MIPI D-PHY ‑yhteensopivaa tulo-/lähtöliitäntää (I/O). MIPI on haastava rajapinta, koska se käyttää sekä epäsymmetristä että differentiaalista signalointia samassa differentiaaliparissa hitaan ja nopean viestinnän lisäksi. MIPI D-PHY -toiminnallisuuden integrointi FPGA I/O -toiminnallisuuteen vähentää piirikortin kompleksisuutta ja pienentää samalla materiaalikustannuksia.

Kun kamerasta saatu kuvavirta on vastaanotettu, referenssimalli muuntaa MIPI CSI-2 RX -muotoisen ulostulon AXI Stream ‑virraksi (Advanced eXtensible Interface). AXI Stream on yksisuuntainen nopea rajapinta, joka tarjoaa datavirtaa isännästä orjalle. Tämä välittää sekä isännän ja orjan välisen tiedonsiirron vaatimat kättelysignaalit (tvalid ja tready) että sivukaistasignaalit. Sivukaistasignaalien avulla voidaan välittää kuvan ajoitustietoja, kuten kehysten aloitus ja tiedonsiirron loppuminen.

AXI Stream sopii erinomaisesti kuvankäsittelysovelluksiin, minkä ansiosta Efinix voi tarjota kuvankäsittelyyn valikoiman IP-ytimiä, jotka voidaan helposti integroida prosessointiketjuun sovelluksen vaatimusten mukaan.

Vastaanottamisen jälkeen MIPI CSI-2 ‑kuvatiedot ja ‑ajastussignaalit muunnetaan AXI Stream ‑virraksi ja syötetään DMA-moduuliin, joka kirjoittaa kuvakehyksen LPDDR4x-muistiin ja toimii kehyspuskurina.

FPGA Sapphire -järjestelmäpiirin (SoC) sisältämä RISC-V-ydin ohjaa tätä DMA-moduulia. Tämä SoC ohjaa kirjoitusta ja esimerkiksi pysäyttää ja käynnistää DMA-kirjoituksen. Lisäksi se antaa DMA-kirjoituskanavalle tarvittavat tiedot kuvatietojen kirjoittamiseen LPDDR4x-muistiin. Tämä sisältää tietoja muistipaikoista sekä tavuina määritellystä kuvan leveydestä ja korkeudesta.

Referenssimallin lähtökanava lukee kuvatiedot LPDDR4x-kehyspuskurista RISC-V SoC-piirin ohjaamana. Tiedot lähetetään DMA IP -ytimestä AXI Stream ‑virtana, joka sitten muunnetaan kennon tarjoamasta RAW-muodosta RGB-muotoon (kuva 2) ja valmistellaan lähtöä varten kortilla olevan Analog Devices ADV7511 ‑HDMI-lähettimen kautta.

Kuva 2: Referenssimallin muodostamia esimerkkikuvia. (Kuvan lähde: Adam Taylor)

Kuva 2: Referenssimallin muodostamia esimerkkikuvia. (Kuvan lähde: Adam Taylor)

DMA-toiminnon käyttö mahdollistaa myös Sapphire SoC RISC-V-ytimelle pääsyn kehyspuskuriin tallennettuihin kuviin sekä abstrakteihin tilastotietoihin ja kuvatietoihin. Sapphire SoC pystyy kirjoittamaan LPDDR4x-muistiin myös peittokuvia, jotka voidaan yhdistää lähtövideovirtaan.

Nykyaikaisissa CMOS-kuva-antureissa (CIS) on useita toimintatiloja, ja ne voidaan määrittää prosessoimaan tietoja itse sirulla ja niille voidaan määrittää useita erilaisia lähtömuotoja ja kellotaajuusvaihtoehtoja. Tämä määritysmahdollisuus tarjotaan yleensä I²C-rajapinnan kautta. Efinixin referenssimallissa Sapphire SoC RISC-V ‑suoritin tarjoaa tämän I²C-tiedonsiirron MIPI-kameroille.

RISC-V-suorittimen integrointi Titanium FPGA-piirille pienentää lopullisen ratkaisun kokoa, sillä se poistaa tarpeen toteuttaa sekä kompleksisia FPGA-tilakoneita, jotka lisäävät suunnitteluriskiä, että ulkoisia suorittimia, jotka lisäävät materiaalikustannuksia.

Suorittimen lisääminen mahdollistaa myös lisätuen kommunikoinnille MicroSD-kortin kanssa. Tämä mahdollistaa reaalimaailman sovellukset, joissa kuvat voidaan joutua tallentamaan myöhempää analyysia varten.

Yleisesti ottaen Ti180-referenssimallin arkkitehtuuri on optimoitu mahdollistamaan pienikokoinen, edullinen mutta suorituskykyinen ratkaisu, jonka avulla kehittäjät voivat vähentää materiaalikustannuksia järjestelmäintegraation keinoin.

Yksi referenssimallien keskeisistä eduista on se, että niitä voidaan käyttää sovelluskehityksen käynnistämiseen mukautetulla laitteistolla, jolloin kehittäjät voivat ottaa mallista tärkeitä elementtejä ja rakentaa niiden päälle tarvitsemansa mukautukset. Tähän sisältyy mahdollisuus käyttää Efinixin TinyML-alustaa FPGA-piirillä suoritettavien konenäköön perustuvien TinyML-sovellusten toteuttamiseen. Tässä voidaan hyödyntää sekä FPGA-logiikan rinnakkaista luonnetta että mahdollisuutta helposti lisätä mukautettuja käskyjä RISC-V-suorittimiin, mikä mahdollistaa kiihdyttimien luomisen FPGA-logiikalla.

Toteutus

Kuten osassa 1 kerrottiin, Efinix-arkkitehtuuri on ainutlaatuinen siinä, että se käyttää XLR-lohkoja sekä reititys- että logiikkatoimintojen tarjoamiseen. Referenssimallin kaltainen videojärjestelmä on sekoitus raskasta logiikkaa ja reititystä: kuvankäsittelyominaisuuksien toteuttamiseen tarvitaan runsaasti logiikkaa, ja lohkojen yhdistäminen vaadituilla taajuuksilla vaatii runsaasti reititystä.

Referenssimalli käyttää noin 42 % laitteen XLR-lohkoista, mikä jättää runsaasti tilaa lisäyksille, mukaan lukien sellaiset räätälöidyt sovellukset kuten Edge-ML.

RAM- ja DSP-lohkojen käyttö on myös erittäin tehokasta, sillä vain neljä 640:stä DSP-lohkosta ja 40 % muistilohkoista on käytössä (kuva 3).

|

Kuva 3: Efinix-arkkitehtuuri varaa XLR-lohkoista vain 42 %, mikä jättää runsaasti tilaa lisäprosesseille. (Kuvan lähde: Adam Taylor)

Laitteen IO-toiminnoissa käytetään LPDDR4x-muistin DDR-rajapintaa, joka tarjoaa Sapphire SoC ‑piirille sovellusmuistin ja kuvien kehyspuskurit. Kaikki laitteelle varatut MIPI-resurssit sekä 50 % vaihelukituista silmukoista ovat käytössä (kuva 4).

|

Kuva 4: Tilannekuva käytetyistä rajapinnoista ja I/O-resursseista. (Kuvan lähde: Adam Taylor)

Yleiskäyttöistä I/O-rajapintaa (GPIO) käytetään I²C-viestintään yhdessä useiden Sapphire SoC ‑piiriin liitettyjen rajapintojen kanssa, kuten NOR FLASH, USB UART ja SD-kortti. HSIO-liitäntää käytetään ADC7511 HDMI ‑lähettimen nopeaan videolähtöön.

Yksi FPGA-suunnittelun keskeisistä elementeistä on se, että pelkästään mallin toteuttaminen ja mahduttaminen FPGA-piirille ei riitä, vaan logiikka on myös pystyttävä toteuttamaan FPGA-piirillä ja saavuttamaan ajoituksessa vaadittu suorituskyky myös reititettynä.

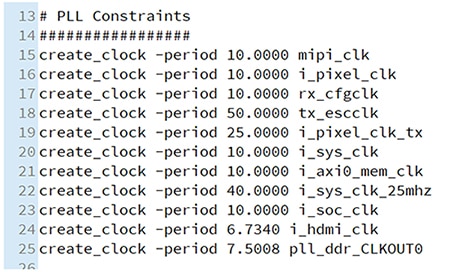

Yhden kellotaajuuden FPGA-ratkaisuiden ajat ovat jo kaukana takana. Ti180-referenssimallissa on useita eri kelloja, jotka kaikki toimivat korkeilla taajuuksilla. Lopullinen ajoitustaulukko näyttää järjestelmän kellojen enimmäistaajuudet. Tässä tapauksessa vaadittu kellotuksen suorituskyky näkyy myös rajoitteissa (kuva 5), joissa HDMI-lähdön kellotaajuus on enintään 148,5 MHz.

Kuva 5: Referenssimallin kellorajoitukset. (Kuvan lähde: Adam Taylor)

Kuva 5: Referenssimallin kellorajoitukset. (Kuvan lähde: Adam Taylor)

Ajoituksen toteuttaminen rajoitusten mukaisesti osoittaa Titanium FPGA XLR -rakenteen potentiaalin, koska se vähentää mahdollista reititysviivettä ja siten parantaa ratkaisun suorituskykyä (kuva 6).

|

Kuva 6: Ajoituksen toteuttaminen rajoitusten mukaisesti osoittaa Titanium FPGA XLR -rakenteen potentiaalin mahdollisen reititysviiveen vähentämisessä, mikä parantaa ratkaisun suorituskykyä. (Kuvan lähde: Adam Taylor)

Yhteenveto

Ti180 M484 ‑referenssimalli esittelee selkeästi Efinixin FPGA-piirien ja erityisesti Ti180-piirin ominaisuuksia. Ratkaisu hyödyntää useita ainutlaatuisia I/O-ratkaisuja kompleksisen kuvankäsittelypolun toteuttamisessa ja tukee useita saapuvia MIPI-virtoja. Tätä kuvankäsittelyjärjestelmää ohjaa ohjelmapohjainen Sapphire SoC ‑järjestelmä, joka toteuttaa sovelluksen tarvitsemat peräkkäiskäsittelyelementit.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.