FPGA:n perusteet – Osa 4: Alkuun Xilinxin FPGA-piireillä

Julkaisija DigiKeyn kirjoittajat Pohjois-Amerikassa

2020-04-01

Toimittajan huomautus: Optimaaliset prosessointiratkaisut saavutetaan usein yhdistämällä RISC- ja CISC-suorittimia ja grafiikkasuorittimia sekä FPGA-piirejä, käyttämällä pelkkiä FPGA-piirejä tai käyttämällä fyysisiä suoritinytimiä sisältäviä FPGA-piirejä. Monet suunnittelijat eivät kuitenkaan tunne FPGA-piirien kykyjä, niiden kehitystä tai sitä, miten niitä voi käyttää. Tämän moniosaisen sarjan osa 1 tarjosi yleisemmän tason johdannon FPGA-piireihin, osa 2 keskittyi Lattice Semiconductorin FPGA-tarjontaan ja osa 3 taas FPGA-laiteperheisiin ja suunnittelutyökaluihin, joiden valmistaja on Microchip Technology (ja sen tytäryhtiö Microsemi Corporation). Tässä osassa 4 aiheena ovat Xilinxin komponentit ja työkalut. Osa 5 kertoo Alteran tuotteista.

Kuten osassa 1 kerrottiin, FPGA-piirit (field-programmable gate array eli ohjelmoitava porttimatriisi) sisältävät monia ominaisuuksia, jotka tekevät niistä korvaamattomia laskentatyökaluja joko yksinään tai monipuolisen arkkitehtuurin osana. Monet suunnittelijat eivät kuitenkaan tunne FPGA-piirejä tai sitä, miten he voisivat käyttää niitä omissa laitteissaan.

Eräs tapa poistaa tämä este on tutustua lähemmin suurten toimittajien tarjoamiin FPGA-arkkitehtuureihin ja työkaluihin. Tässä artikkelissa tutustutaan Xilinxin mallistoon.

Korkean tason yleiskatsaus FPGA-vaihtoehtoihin

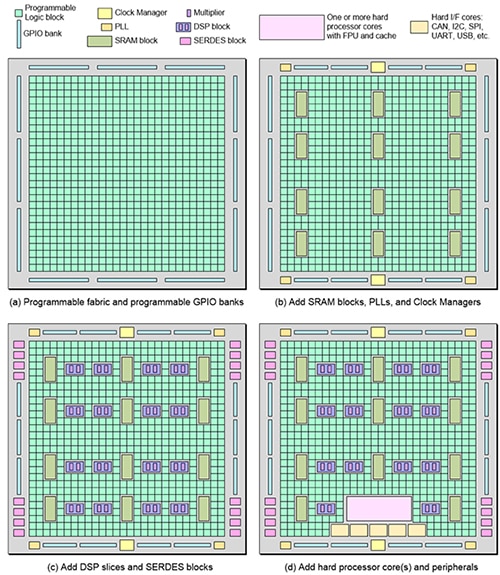

Markkinoilla on monia erityyppisiä FPGA-piirejä, joista jokaisessa on erilaisia kykyjen ja toimintojen yhdistelmiä. Jokaisen FPGA-piirin ytimessä on ohjelmoitava rakenne. Tämä esitetään ryhmänä ohjelmoitavia logiikkalohkoja, joita kutsutaan myös logiikkaelementeiksi (LE) (kuva 1a). Seuraavalla tasolla FPGA-rakenteeseen kuuluu SRAM-lohkoja, joita kutsutaan block RAM:iksi (BRAM), vaihelukittuja silmukoita (PLL) ja kellon hallintamoduuleja (kuva 1b). Siihen voidaan lisätä myös digitaalista signaalinkäsittelyä (DSP) tarjoavia lohkoja (DSP slice) sekä nopeita sarja-/rinnakkaismuunninlohkoja (SERDES) (kuva 1c).

Kuva 1: Yksinkertaisimmat FPGA-piirit sisältävät vain ohjelmoitavan rakenteen sekä määritettävän yleiskäyttöisen IO-väylän (GPIO) (a); eri arkkitehtuureissa tähän lisätään SRAM-lohkoja; PLL-silmukoita sekä kellon hallintamoduuleja (b); DSP-lohkoja ja SERDES-rajapintoja (c) sekä perinteisiä suoritinytimiä ja lisälaitteita (d). (Kuvan lähde: Max Maxfield)

Kuva 1: Yksinkertaisimmat FPGA-piirit sisältävät vain ohjelmoitavan rakenteen sekä määritettävän yleiskäyttöisen IO-väylän (GPIO) (a); eri arkkitehtuureissa tähän lisätään SRAM-lohkoja; PLL-silmukoita sekä kellon hallintamoduuleja (b); DSP-lohkoja ja SERDES-rajapintoja (c) sekä perinteisiä suoritinytimiä ja lisälaitteita (d). (Kuvan lähde: Max Maxfield)

Lisälaitteiden rajapinnat kuten CAN, I2C, SPI, UART ja USB voidaan toteuttaa ohjelmoitavina ytiminä rakenteeseen, mutta monissa FPGA-piireissä ne ovat mukana fyysisinä ytiminä. Vastaavasti myös mikroprosessorit voidaan toteuttaa ohjelmoitavaan rakenteeseen tai fyysisinä ytiminä (kuva 1d). Fyysisillä suoritinytimillä varustettuja FPGA-piirejä kutsutaan FPGA-järjestelmäpiireiksi (SoC). Erilaiset FPGA-piirit tarjoavat erilaisia toimintoja, ominaisuuksia ja kykyjä, jotka on tarkoitettu erilaisille markkinoille ja eri käyttötarkoituksiin.

FPGA-valmistajia on useita, kuten Altera (jonka Intel osti), Atmel (jonka Microchip Technology osti), Efinix, Lattice Semiconductor, Microsemi (Microchip Technology osti myös tämän) ja Xilinx.

Kaikki nämä valmistajat tarjoavat useita FPGA-tuoteperheitä. Osa tarjoaa SoC FPGA -piirejä, toiset taas tekoälyn (AI) ja koneoppimisen (ML) sovelluksiin tarkoitettuja tuotteita, jotkin taas avaruuden kaltaisiin runsasta säteilyä sisältäviin ympäristöihin tarkoitettuja säteilynkestäviä laitteita. Parhaan laitteen valinta kuhunkin tehtävään voi olla vaikeaa, sillä laiteperheitä on useita ja jokainen niistä tarjoaa erilaiset ominaisuudet.

Esittelyssä Xilinxin FPGA-, SoC-, MPSoC-, RFSoC- sekä ACAP-piirit

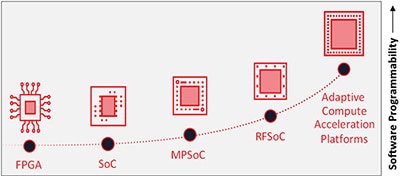

Xilinxin tarjoamien ohjelmoitavien laitteiden mallisto yltää vaatimattomista aina erittäin tehokkaisiin laitteisiin asti. Tarjolla on perinteisiä FPGA-piirejä sekä SoC-piirejä (ohjelmoitava FPGA-rakenne sekä yksi kiinteä suoritinydin), MPSoC-piirejä (ohjelmoitava FPGA-rakenne sekä useita kiinteitä suoritinytimiä), RFSoC-piirejä (MPSoC-piirejä RF-ominaisuuksilla) ja ACAP-piirejä (mukautuvia laskennan nopeutusalustoja) (kuva 2).

Kuva 2: Ajan myötä Xilinxin arkkitehtuurivalikoima on kehittynyt yksinkertaisista, vain ohjelmoitavan rakenteen sisältävistä FPGA-piireistä SoC-laitteisiin, joissa ohjelmoitavaa rakennetta tehostetaan kiinteällä suoritinytimellä, sekä useita suorittimia sisältäviin MPSoC-piireihin, RF-ominaisuuksilla varustettuihin RFSoC-piireihin sekä uusimman sukupolven ACAP-piireihin, jotka on tarkoitettu tekoälyn kaltaisiin sovelluksiin. (Kuvan lähde: Max Maxfield)

Kuva 2: Ajan myötä Xilinxin arkkitehtuurivalikoima on kehittynyt yksinkertaisista, vain ohjelmoitavan rakenteen sisältävistä FPGA-piireistä SoC-laitteisiin, joissa ohjelmoitavaa rakennetta tehostetaan kiinteällä suoritinytimellä, sekä useita suorittimia sisältäviin MPSoC-piireihin, RF-ominaisuuksilla varustettuihin RFSoC-piireihin sekä uusimman sukupolven ACAP-piireihin, jotka on tarkoitettu tekoälyn kaltaisiin sovelluksiin. (Kuvan lähde: Max Maxfield)

Xilinxin tuotevalikoima on niin laaja, kattaa niin monia markkinasegmenttejä ja tarjoaa niin monipuolisen valikoiman toteutustapoja, että vasta FPGA-piireihin tutustuvan voi olla vaikea ymmärtää sen koko kuvaa.

Xilinx toimii muun muassa seuraavilla markkina-alueilla, niihin kuitenkaan rajoittumatta: konesalit (laskenta, verkko, tallennus), viestintä (langallinen ja langaton), ilmailu sekä puolustus, teollisuus-, tiede- ja lääketiedesovellukset (ISM), testaus-, mittaus- ja emulaatiosovellukset (TME) sekä autoteollisuus, lähetysala ja kuluttajatuotteet.

Toteutustapoihin kuuluvat piirit, arviointialustat ja kehityssarjat, joita Xilinx kutsuu laitteistosovitettaviksi laitteiksi; järjestelmämoduulit (SoM) ja PCIe-kiihdytinkortit, joita kutsutaan käyttöönotettaviksi loppujärjestelmiksi, sekä FPGA palveluna -ratkaisut (FAAS), jotka käsittävät Xilinxin teknologioiden arvioinnin ja hyödyntämisen johtavien pilvipalvelun tarjoajien, kuten Amazon Web Servicesin (AWS), Alibaba.comin ja Nimbix.netin kautta.

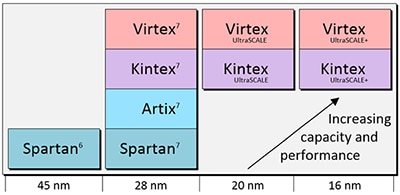

Eräs tapa luokitella Xilinxin FPGA-tarjontaa on käyttää perusteena valmistusprosessiteknologiaa (kuva 3).

Kuva 3: Xilinxin FPGA-mallisto tarjoaa kattavan valikoiman eri prosessiteknologioita, joka vastaa erilaisten sovelluksien tarpeisiin . (Kuvan lähde: Max Maxfield)

Kuva 3: Xilinxin FPGA-mallisto tarjoaa kattavan valikoiman eri prosessiteknologioita, joka vastaa erilaisten sovelluksien tarpeisiin . (Kuvan lähde: Max Maxfield)

Kohdesovelluksesta riippuen suunnittelijat voivat valita aiemmalla teknologialla toteutetun edullisen ja pienen FPGA-piirin, tai esimerkiksi huippuluokan verkkosovellusta varten suuren kapasiteetin, kaistanleveyden ja suorituskyvyn tarjoavan laitteen, joka on toteutettu uudemmalla teknologialla.

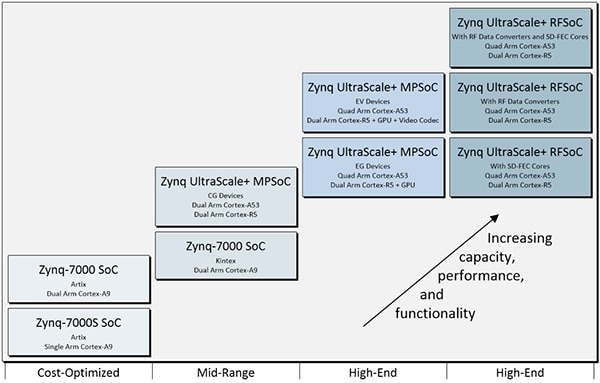

Mikäli laitteessa tarvitaan yksi tai useampia kiinteitä suoritinytimiä (ja muita lisätoimintoja kuten grafiikkasuorittimia, koodekkeja ja pehmeitä päätöksiä käyttävää etenemisvirheen korjausta (SD-FEC) tukevia ytimiä), Xilinx tarjoaa valikoiman laitteita Zynq-tuoteperheen alla. Kuvassa 4 esitetään yhteenveto Zynq-tuoteperheen SoC-, MPSoC- ja RFSoC-tarjonnasta. Nämä ratkaisut tarjoavat suunnittelijoille laajan valikoiman ominaisuuksia tehon, suorituskyvyn, kustannusten ja markkinoilletuontiajan optimoimiseksi.

Kuva 4: Xilinxin SoC-, MPSoC- ja RFSoC-tarjonta integroi suoritinohjelmiston ohjelmoitavuuden FPGA-piirin laitteisto-ohjelmointiin. Tämä tarjoaa suunnittelijoille suorituskykyä, joustavuutta ja skaalautuvuutta. (Kuvan lähde: Max Maxfield)

Kuva 4: Xilinxin SoC-, MPSoC- ja RFSoC-tarjonta integroi suoritinohjelmiston ohjelmoitavuuden FPGA-piirin laitteisto-ohjelmointiin. Tämä tarjoaa suunnittelijoille suorituskykyä, joustavuutta ja skaalautuvuutta. (Kuvan lähde: Max Maxfield)

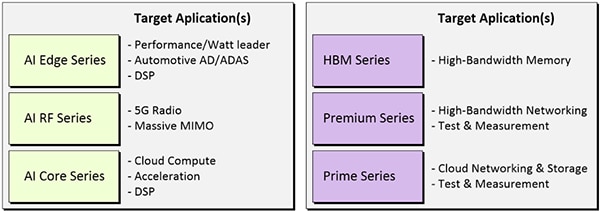

Uusimmat Xilinx-tuotteet ovat Versal-sarjan mukautuvat laskentakiihdytysalustat (ACAP), jotka on kaikki toteutettu 7 nanometrin (nm) prosessiteknologialla. ACAP-piirit ovat erittäin integroituja moniytimisiä laskenta-alustoja, jotka voivat mukautua kehittyviin ja monentyyppisiin algoritmeihin. Niitä voidaan muokata dynaamisesti laitteisto- ja ohjelmistotasolla ja ne sopivat moniin eri sovelluksiin ja työkuormiin. Sekä laitteistosuunnittelijoiden että ohjelmistokehittäjien on helppo ohjelmoida ohjelmoitavaan verkkopiiriin (NoC) perustuvia ACAP-piirejä.

Versal-laitteiden uusia ominaisuuksia ovat muun muassa intelligent engine -yksiköt (suuri määrä ML- ja DSP-laskentaan tarkoitettuja vektorisuorittimia), suuren kaistanleveyden ja alhaisen latenssin vähävirtainen NoC, joka pystyy siirtämään teratavukaupalla tietoa, sekä integroitu kuori, joka tarjoaa paremman suorituskyvyn, hyötysuhteen ja tuottavuuden valmiin ydininfrastruktuurin ja järjestelmäyhteyksien avulla.

Kuvassa 5 esitetään yleiskatsaus Versal ACAP -mallistosta.

Kuva 5: Xilinx Versal -ACAP-piirit ovat erittäin integroituja moniytimisiä laskenta-alustoja, jotka voivat mukautua kehittyviin ja monentyyppisiin algoritmeihin. ACAP-piirejä voidaan muokata dynaamisesti laitteisto- ja ohjelmistotasolla ja ne sopivat moniin eri sovelluksiin ja työkuormiin. (Kuvan lähde: Max Maxfield)

Kuva 5: Xilinx Versal -ACAP-piirit ovat erittäin integroituja moniytimisiä laskenta-alustoja, jotka voivat mukautua kehittyviin ja monentyyppisiin algoritmeihin. ACAP-piirejä voidaan muokata dynaamisesti laitteisto- ja ohjelmistotasolla ja ne sopivat moniin eri sovelluksiin ja työkuormiin. (Kuvan lähde: Max Maxfield)

Kuten suunnittelutyökaluja koskevassa osiossa todetaan, Versal-laitteisiin liittyvä uusi ohjelmistopino on tärkeä erottautumistekijä. Se on tarkoitettu datatutkijoille ja ohjelmistosuunnittelijoille sekä perinteisille laitteistosuunnittelijoille.

Nykyisin on saatavana lukemattomia Xilinx-laitteita. Muutamia hyviä esimerkkejä ovat Artix-7 FPGA, Kintex UltraScale FPGA, Kintex UltraScale+ FPGA, Trenz Electronic GmbH:n Zynq-7000-SoC-moduuli sekä Zynq UltraScale+ MPSoC.

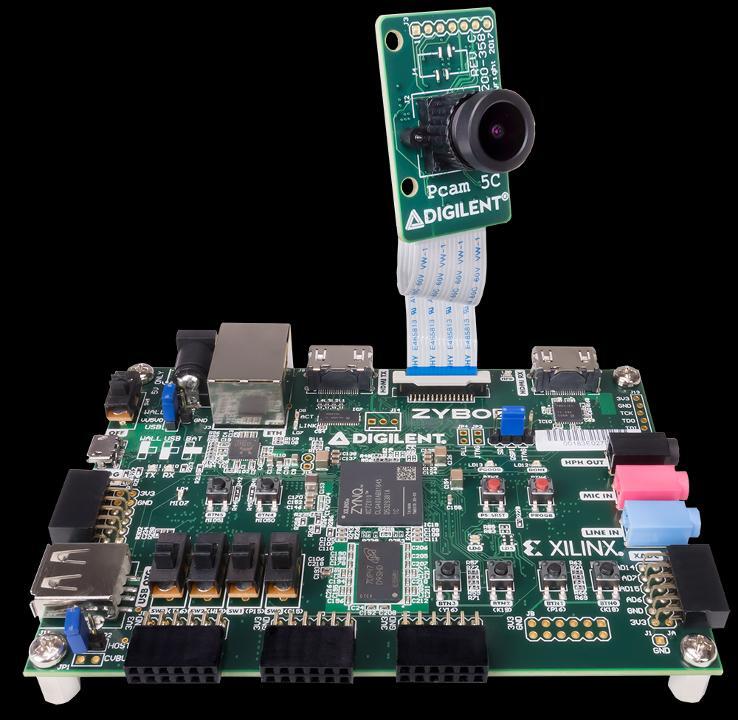

Samalla tavoin saatavana on laaja valikoima arviointi- ja kehitysalustoja. Hyviä esimerkkejä niistä ovat Digilentin Artix-7-FPGA-arviointialusta, Analog Devicesin Kintex UltraScale -FPGA-arviointialusta, Xilinxin Kintex UltraScale+ -FPGA-arviointialusta, Digilentin Zynq-7000-SoC-FPGA-arviointialusta sekä Xilinxin Zynq UltraScale+ -MPSoC-FPGA-arviointialusta.

Suunnittelu ja tuotekehitys Xilinxin FPGA-, SoC- ja ACAP-piireillä

Eräs alue, jossa Xilinx todella erottuu kilpailijoistaan, on sen suunnittelutyökalujen ja -työnkulkujen kattavuus.

Tämän FPGA-piirejä koskevan sarjan 1. osassa kerroimme, että perinteinen tapa suunnitella näitä laitteita on sellainen, että suunnittelijat käyttävät laitteistokuvauskieltä (HDL), kuten Verilogia tai VHDL-kieltä kuvatakseen suunnitelman rekisterisiirtotasoksi (RTL) kutsutulla abstraktiotasolla. Näitä RTL-kuvauksia voidaan ensin simuloida niiden oikean toiminnan varmistamiseksi, minkä jälkeen ne siirretään synteesityökaluun, joka luo FPGA-piirin ohjelmointiin käytettävän konfiguraatiotiedoston.

Seuraava abstraktiotaso on laitesuunnitelman laatiminen C/C++:n kaltaisella ohjelmointikielellä tai SystemC:n kaltaisella erikoistoteutuksella, jonka C++-luokkien ja -makrojen valikoimalla voidaan luoda tapahtumapohjainen simulaatiorajapinta. Ne helpottavat C++-syntaksilla kuvattujen yhtäaikaisten prosessien simulointia. Tällaisia kuvauksia voidaan analysoida ja profiloida suorittamalla niitä tavallisten ohjelmien tapaan, minkä jälkeen ne siirretään korkean tason synteesirutiinille (HLS), jonka tuottama RTL syötetään puolestaan tavanomaiselle synteesirutiinille.

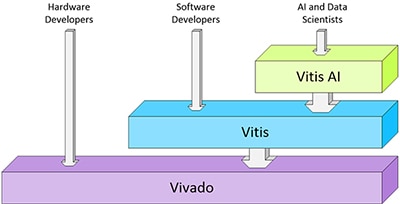

Vivado Design Suite HLx Edition -versiot tarjoavat kaiken tämän toiminnallisuuden, jonka lopputuotteena syntyvä määritysbittivirta ladataan kohteena olevaan FPGA-, SoC-, MPSoC-, RFSoC- tai ACAP-laitteeseen. Sen lisäksi, että laitteistokehittäjät voivat hyödyntää C-pohjaista suunnittelua ja optimoitua uudelleenkäyttöä, Vivado tarjoaa myös uudelleenkäytettävän IP-alijärjestelmän, integroinnin automatisoinnin sekä suunnittelun nopeutetun viimeistelyn (kuva 6).

Kuva 6: Korkean tason näkymä Xilinx Vivado- ja Vitis-suunnittelutyökaluihin osoittaa, miten ne auttavat käyttäjää työskentelemään sopivimmalla abstraktiotasolla. Laitteistosuunnittelijat käyttävät Vivadoa, ohjelmistokehittäjät käyttävät Vitisiä ja tekoäly- sekä datatukijat käyttävät Vitis AI -työkalua. (Kuvan lähde: Max Maxfield)

Kuva 6: Korkean tason näkymä Xilinx Vivado- ja Vitis-suunnittelutyökaluihin osoittaa, miten ne auttavat käyttäjää työskentelemään sopivimmalla abstraktiotasolla. Laitteistosuunnittelijat käyttävät Vivadoa, ohjelmistokehittäjät käyttävät Vitisiä ja tekoäly- sekä datatukijat käyttävät Vitis AI -työkalua. (Kuvan lähde: Max Maxfield)

Seuraavaa abstraktiotasoa tukee Vitis Unified Software Platform, joka antaa ohjelmistokehittäjille mahdollisuuden rakentaa kiihdytettyjä sovelluksia saumattomasti. Konseptitasolla Vitisin ”päällä” toimii Vitis AI, jonka avulla tekoäly- ja datatutkijat voivat toimia TensorFlow-abstraktiotasolla. Vitis AI on kehitysalusta tekoälypäättelylle Xilinxin laitealustoilla, sisältäen sekä reunalaitteet että Alveo PCIe -kortit. Se koostuu optimoidusta IP:stä, työkaluista, kirjastoista, malleista ja esimerkkisuunnitelmista ja se on suunniteltu hyödyntämään Xilinxin FPGA- ja ACAP-laitteiden täysi potentiaali tekoälyn kiihdyttämiseen.

Vivadon syötteenä on Vitis minkä syötteenä on Vitis AI. Kuvan 6 tärkein opetus on se, että käyttäjät näkevät vain sen verran kuin on tarpeen. Laitteistokehittäjät ”näkevät” vain Vivadon, ohjelmistokehittäjät vain Vitisin ja tekoäly- sekä datatutkijat vain Vitis AI:n. Näin käyttäjät voivat käyttää sopivimman abstraktiotason työkaluja.

Ohjelmistokehittäjille tarjottava Vitisin kaltainen työkalu, joka erottaa kehityksen laitteistotasosta, tuo FPGA-piirit paljon suuremman kehittäjäjoukon ulottuville. Samalla tavoin tekoäly- ja datatutkijoille tarkoitettu Vitis AI:n kaltainen työkalu, jolla he voivat keskittyä omaan abstraktiotasoonsa alla toimivan ohjelmiston sijaan, laajentaa FPGA-piirien käyttömahdollisuuksia entisestään.

Tarjotessaan näitä mahdollisuuksia Xilinx johtaa koko alan laajuista kampanjaa, jolla FPGA-työkalujen abstraktiotasoa pyritään nostamaan. Näin kehittäjät voivat helpommin hyödyntää laitteiden kykyjä ja integroida niitä omiin laitteisiinsa.

Yhteenveto

Optimaaliset prosessointiratkaisut saavutetaan usein yhdistämällä suorittimia ja FPGA-piirejä, käyttämällä pelkkiä FPGA-piirejä tai käyttämällä fyysisiä suoritinytimiä sisältäviä FPGA-piirejä. FPGA-teknologia on kehittynyt nopeasti viime vuosina, ja mitä joustavuuteen, käsittelynopeuteen ja tehoon tulee, se voi vastata moniin suunnitteluvaatimuksiin. Näin FPGA-piirit ovat erittäin hyödyllisiä moniin sovelluksiin älykkäistä rajapinnoista konenäköön ja tekoälyyn asti.

Kuten artikkelissa esitetään, Xilinxin tarjoamien ohjelmoitavien laitteiden mallisto yltää vaatimattomista aina erittäin tehokkaisiin laitteisiin asti. Tarjolla on niin perinteisiä FPGA-piirejä kuin SoC-piirejä (ohjelmoitava FPGA-rakenne sekä yksi kiinteä suoritinydin), MPSoC-piirejä (ohjelmoitava FPGA-rakenne sekä useita kiinteitä suoritinytimiä), RFSoC-piirejä (MPSoC-piirejä RF-ominaisuuksilla) sekä ACAP-piirejä (mukautuvia laskennan nopeutusalustoja).

Helpottaakseen laitteiden käyttöä suunnittelussa Xilinx tarjoaa valikoiman työkaluja, joilla voidaan vastata laitteistokehittäjien (Vivado), ohjelmistokehittäjien (Vitis) sekä tekoäly- ja datatutkijoiden (Vitis AI) tarpeisiin.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.