Käytä FPGA-piirejä nopeuttamaan suuritehoisten ja vähävirtaisten AI-sovellusten kehitystä reunalla

Julkaisija DigiKeyn kirjoittajat Pohjois-Amerikassa

2021-01-12

Suunnittelijat, jotka haluavat käyttää tekoäly (AI) -algoritmeja reunan päättelyprosessoreissa, ovat jatkuvan paineen alla vähentää virrankulutusta ja kehitysaikaa, vaikka prosessointivaatimukset kasvavatkin. Ohjelmoitavat porttimatriisit (FPGA) tarjoavat erityisen tehokkaan kombinaation halutessa nopeutta ja korkeaa hyötysuhdetta ja toteutettaessa AI-reunatekoälyn vaatimia neuroverkkojen (NN) päättelykoneita. Perinteiset FPGA-kehitysmenetelmät voivat kuitenkin näyttää kompleksisilta kehittäjistä, jotka eivät ole tuttuja FPGA-piirien kanssa. Tästä syystä kehittäjät kääntyvät usein vähemmän optimaalisien ratkaisuiden puoleen.

Tässä artikkelissa kuvataan yksinkertaisempaa lähestymistapaa yritykseltä Microchip Technology, minkä avulla kehittäjät voivat ohittaa perinteisen FPGA-kehityksen ja luoda koulutettuja NN-verkkoja FPGA-piirejä varten. Tämä sisältää myös ohjelmistokehityssarjan (SDK) sekä FPGA-pohjaisen videosarjan, jonka avulla älykkään sulautetun näkösovelluksen kehitys voidaan aloittaa välittömästi.

Miksi käyttää reunalla tekoälyä?

Reunalaskenta tarjoaa paljon etuja Esineiden internet (IoT) -sovelluksiin useilla sovellusalueilla, mm. teollisuusautomaatio, turvallisuusjärjestelmät, älykodit ja niin edelleen. Tuotantotiloihin tarkoitetuissa Teollisuus IoT (IIoT) -sovelluksessa reunalaskenta voi dramaattisesti parantaa prosessinohjaussilmukoiden vasteaikaa eliminoimalla edestakaiset viiveet pilvipohjaisiin sovelluksiin. Vastaavasti reunapohjainen turvallisuusjärjestelmä tai älykodin ovilukko voi jatkaa toimintaansa silloinkin kun yhteys pilveen tahattomasti tai tahallisesti katkeaa. Monissa tapauksissa reunalaskennan käyttö kaikissa näissä sovelluksissa voi laskea kokonaiskäyttökustannuksia vähentämällä tuotteen riippuvuutta pilviresursseista. Sen sijaan että kehittäjät joutuisivat odottamattomasti käyttämään kalliita pilvilisäresursseja jos tuotteiden kysyntä kasvaa, kehittäjät voivat luottaa tuotteiden paikalliseen prosessointikapasiteettiin. Tämä pitää käyttökustannukset vakaampina.

Koneoppimisen (ML) päättelymallien nopea hyväksyminen ja kasvanut kysyntä korostaa dramaattisesti reunalaskennan tärkeyttä. Kehittäjien kannalta päättelymallien paikallinen prosessointi vähentää vasteen latenssia sekä pilvipohjaiseen päättelyyn vaadittavien pilviresurssien kustannuksia. Käyttäjien kannalta paikallisten päättelymallien käyttö lisää luottamusta siihen, että heidän tuotteensa jatkavat toimintaa hetkellisestä Internet-yhteyden katkeamisesta tai tuotteen myyjän pilvipohjaisiin tuotteisiin tekemistä muutoksista riippumatta. Lisäksi turvallisuutta ja yksityisyyttä koskevat kysymykset saattavat lisätä paikallisen prosessoinnin ja päättelyn tarvetta, koska tällä rajoitetaan arkaluonteisien tietojen lähettämistä pilveen julkisen Internetin kautta.

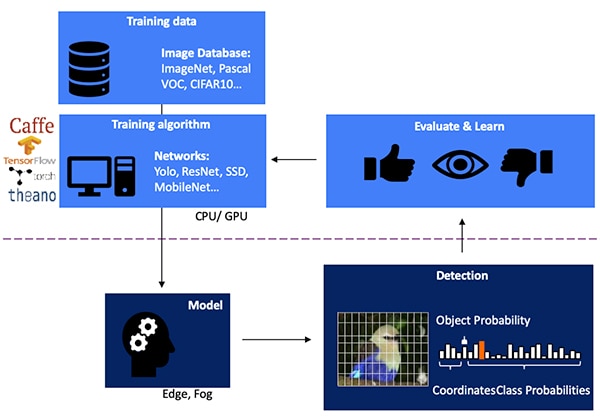

NN-päättelymallin kehittäminen näköpohjaista objektin tunnistamista varten on monivaiheinen prosessi, joka alkaa mallin kouluttamisesta. Tämä suoritetaan tyypillisesti ML-ympäristössä, esimerkkinä TensorFlow, ja siinä käytetään julkisesti saatavana olevia luokiteltuja kuvia tai omia luokiteltuja kuvia. Prosessointivaatimuksista johtuen mallin kouluttaminen suoritetaan tyypillisesti grafiikkasuorittimilla (GPU) pilvessä tai muussa suuritehoisessa laskenta-alustassa. Sen jälkeen kun koulutus on suoritettu, malli muunnetaan päättelymalliksi, jota voidaan käyttää reuna- tai sumulaskentaresursseissa. Nämä antavat päättelyn tulokset joukkona objektiluokkatodennäköisyyksiä (kuva 1).

Kuva 1: Päättelymallin toteuttaminen AI-reunatekoälyä varten on monivaiheisen prosessin lopussa. Prosessi vaatii NN-verkkojen kouluttamista ja optimointia NN-alustoissa käyttäen saatavana olevaa tai muokattua koulutusdataa. (Kuvan lähde: Microchip Technology)

Kuva 1: Päättelymallin toteuttaminen AI-reunatekoälyä varten on monivaiheisen prosessin lopussa. Prosessi vaatii NN-verkkojen kouluttamista ja optimointia NN-alustoissa käyttäen saatavana olevaa tai muokattua koulutusdataa. (Kuvan lähde: Microchip Technology)

Miksi päättelymallit ovat laskennallisesti haastavia

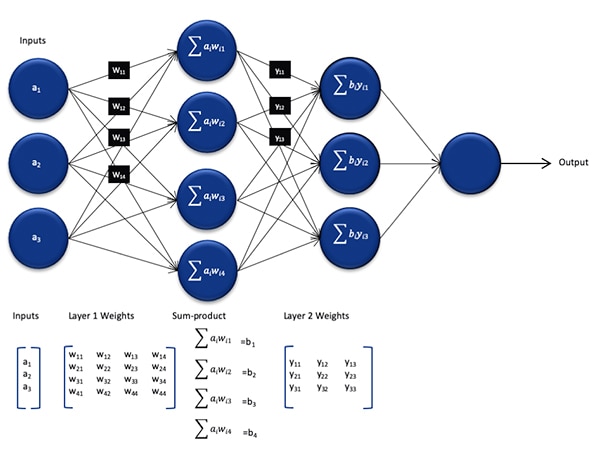

Vaikka NN-päättelymalli on kooltaan pienempi ja vähemmän kompleksinen kuin koulutusprosessissa käytetty malli, se on kuitenkin yleisprosessoreille laskennallisesti haastava, koska se vaatii runsaasti laskentaa. Syvä NN-verkko muodostuu yleisessä muodossa useista kerroksista neuronijoukkoja. Täysin yhdistetyssä verkossa jokaisen kerroksen jokaisen neuronin nij on laskettava summa kaikkien tulojen kertomalla saaduista tuloista käyttäen näihin liittyviä painokertoimia wij (kuva 2).

Kuva 2: NN-päättelyn vaatimien laskutoimitusten lukumäärä voi muodostaa merkittävän laskennallisen kuorman. (Kuvan lähde: Microchip Technology)

Kuva 2: NN-päättelyn vaatimien laskutoimitusten lukumäärä voi muodostaa merkittävän laskennallisen kuorman. (Kuvan lähde: Microchip Technology)

Kuvassa 2 ei näytetä laskennallisia lisävaatimuksia, jotka aiheutuvat aktivointifunktiosta, joka muokkaa jokaisen neuronin lähtöä kuvaamalla negatiiviset arvot nollaksi ja kuvaamalla arvoa 1 suuremmat arvot arvoksi 1, eikä vastaavia funktioita. Kunkin neuronin nij aktivointifunktion lähtö toimii seuraavan kerroksen i+1 tulona. Tätä jatketaan jokaiselle kerrokselle. Lopuksi NN-mallin lähtökerros tarjoaa lähtövektorin, joka kuvaa todennäköisyyttä, että alkuperäinen tulovektori (tai matriisi) vastaa yhtä luokista (tai merkeistä), joita ohjatun oppimisen prosessissa käytettiin.

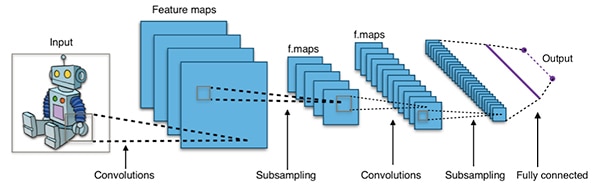

Todelliset NN-mallit rakennetaan käyttäen arkkitehtuurimuotoja, jotka ovat paljon suurempia ja kompleksisempia kuin ylhäällä olevassa kuvassa esitetty yleinen NN-arkkitehtuuri. Esimerkiksi tyypillinen konvoluutio-NN (CNN), jota käytetään objektin tunnistukseen kuvasta, soveltaa näitä periaatteita vaihe vaiheelta ja skannaa tulokuvan leveyden, korkeuden ja värisyvyyden sekä tuottaa joukon ominaisuuskarttoja, jotka lopulta antavat lähdön todennäköisyysvektorin (kuva 3).

Kuva 3: Objektin tunnistuksessa kuvasta käytettävät CNN-verkot sisältävät suuren määrän neuroneja ja useita kerroksia, mikä asettaa enemmän vaatimuksia laskenta-alustalle. (Kuvan lähde: Aphex34 CC BY-SA 4.0)

Kuva 3: Objektin tunnistuksessa kuvasta käytettävät CNN-verkot sisältävät suuren määrän neuroneja ja useita kerroksia, mikä asettaa enemmän vaatimuksia laskenta-alustalle. (Kuvan lähde: Aphex34 CC BY-SA 4.0)

NN-laskennan nopeutus käyttämällä FPGA-piirejä

Vaikka useita vaihtoehtoja tulee jatkuvasti lisää päättelymallien suorittamiseksi reunalla, vain harvat vaihtoehdot tarjoavat optimaalisen yhdistelmän joustavuutta, suorituskykyä ja korkean hyötysuhteen, joita tarvitaan käytännössä suuren nopeuden päättelyssä reunalla. AI-reunatekoälyyn valmiina saatavista vaihtoehdoista yksi on FPGA. Ne ovat erityisen tehokkaita, koska ne tarjoavat suuritehoisen laitteistopohjaisen suorituksen laskentaintensiivisten operaatioiden suoritukseen ja kuluttavat suhteellisen vähän virtaa.

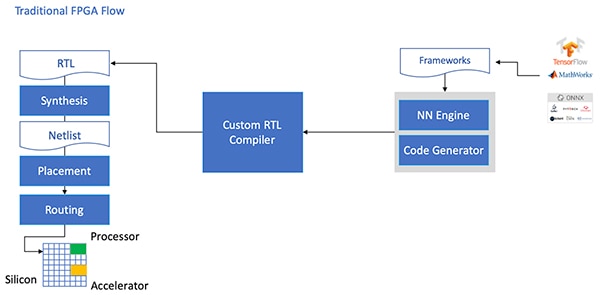

Vaikka FPGA-piirit tarjoavat lukuisia etuja, ne joskus jätetään huomiotta, koska perinteinen kehitysmalli voi olla pelottava kehittäjistä, joilla ei ole paljoa kokemusta FPGA-piireistä. Jotta kehittäjä voisi luoda tehokkaan FPGA-toteutuksen NN-alustassa generoidusta NN-mallista, kehittäjän on ymmärrettävä hienoudet, joita liittyy mallin muuntamiseen RTL-kieleksi (Register Transfer Language ), mallin syntetisointiin sekä fyysiseen reititys-ja-sijoitus-suunnitteluvaiheeseen optimoidun toteutuksen saamiseksi (kuva 4).

Kuva 4: Toteuttaakseen NN-mallin FPGA-piirillä kehittäjien on tähän saakka täytynyt ymmärtää miten muuttaa malli RTL-kieleksi ja käydä läpi perinteinen FPGA-kehitysprosessi. (Kuvan lähde: Microchip Technology)

Kuva 4: Toteuttaakseen NN-mallin FPGA-piirillä kehittäjien on tähän saakka täytynyt ymmärtää miten muuttaa malli RTL-kieleksi ja käydä läpi perinteinen FPGA-kehitysprosessi. (Kuvan lähde: Microchip Technology)

Microchip Technology tarjoaa ratkaisun yrityksen PolarFire-FPGA-piireillä, erityisellä ohjelmistolla sekä näihin liittyvillä immateriaalioikeuksilla (IP). Nämä tekevät suuritehoisesta ja vähävirtaisesta päättelystä reunalla helppokäyttöistä myös kehittäjille, joilla ei ole kokemusta FPGA-piireistä.

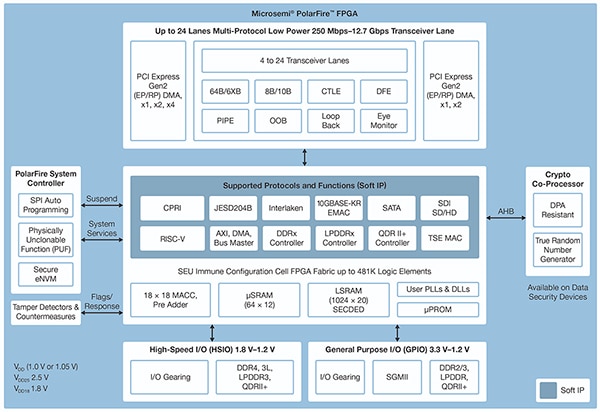

PolarFire FPGA -piirit on valmistettu käyttäen kehittynyttä ei-volatiilista prosessiteknologiaa ja ne on suunniteltu maksimoimaan joustavuus ja suorituskyky samalla kun ne minimoivat virrankulutuksen. Ne tarjoavat suuren määrän suurnopeusliitäntöjä kommunikointia ja tuloja/lähtöjä (I/O) varten ja ne tarjoavat syvän FPGA-rakenteen, joka tukee kehittynyttä toiminnallisuutta käyttäen ohjelmistollisia IP-ytimiä, mukaan lukien RISC-V-prosessorit, kehittyneet muistikontrollerit sekä muut tavalliset rajapinta-alijärjestelmät (kuva 5).

Kuva 5: Microchip Technology PolarFire -arkkitehtuuri tarjoaa syvän rakenteen, joka on suunniteltu vastaamaan suuritehoisten suunnitelmien vaatimuksia, mukaan lukien laskentaintensiivisten päättelymallien toteutus. (Kuvan lähde: Microchip Technology)

Kuva 5: Microchip Technology PolarFire -arkkitehtuuri tarjoaa syvän rakenteen, joka on suunniteltu vastaamaan suuritehoisten suunnitelmien vaatimuksia, mukaan lukien laskentaintensiivisten päättelymallien toteutus. (Kuvan lähde: Microchip Technology)

PolarFire FPGA -rakenne tarjoaa laajan joukon logiikkaelementtejä ja erityslohkoja, joita kapasiteetiltaan erilaiset PolarFire FPGA -perheen jäsenet tukevat, mukaan lukien MPF100T-, MPF200T-, MPF300T- ja MPF500T-sarjat (taulukko 1).

|

Taulukko 1: PolarFire-sarja tarjoaa erilaisia FPGA-rakenteita ja kapasiteetteja. (Taulukon lähde: DigiKey, perustuu Microchip Technology PolarFiren teknisiin tietoihin)

PolarFire-arkkitehtuuri sisältää erityisen kiinnostavia ominaisuuksia päättelyn nopeuttamiseksi, mm. dedikoitu matematiikkalohko, joka tarjoaa 18 bittiä × 18 bittiä etumerkillisen kertolasku-akkumulointi-funktion (MAC) etukäteis-yhteenlaskurilla. Sisäänrakennettu pistetulotila käyttää yhtä matematiikkalohkoa suorittaakseen kaksi 8-bittistä kerto-operaatiota. Tämä tarjoaa mekanismin, joka lisää kapasiteettia hyödyntämällä mallin kvantisoinnin häviävän pientä vaikutusta tarkkuuteen.

Sen lisäksi että PolarFire nopeuttaa matemaattisia operaatioita, siinä käytettävä arkkitehtuuri vähentää sellaisia muistiin liittyviä pullonkauloja, joita yleiskäyttöisissä arkkitehtuureissa esiintyy päättelymallitoteutuksissa. Esimerkkinä tästä toimivat pienet jaetut muistit, joihin tallennetaan NN-algoritmin suorituksen aikana generoidut välitulokset. Myös NN-mallin painokertoimet ja biasarvot voidaan tallentaa 16 x 18 -bittiseen kertoimille tarkoitettuun pelkästään luettavaan ROM (Read-Only Memory) -muistiin, joka on rakennettu matematiikkalohkoa lähellä sijaitsevista logiikkaelementeistä.

Yhdessä muiden PolarFire FPGA -rakenteen ominaisuuksien kanssa matematiikkalohkot tarjoavat perustan Microchip Technologyn ylemmän tason CoreVectorBlox IP-ominaisuuksille. Tämä toimii joustavana NN-moottorina, jolla voidaan suorittaa erityyppisiä NN-verkkoja. CoreVectorBlox IP sisältää joukon ohjausrekistereitä sekä kolme merkittävää toimilohkoa:

- Mikrokontrolleri: Yksinkertainen ohjelmallinen RISC-V-prosessori, joka lukee Microchipin laiteohjelmiston BLOB (Binary Large OBject) -tiedoston sekä käyttäjäkohtaisen NN-BLOB-tiedoston ulkoisesta tallennuslaitteesta. Tämä ohjaa kaikkia CoreVectorBloxin toimintoja suorittamalla käskyjä laiteohjelmisto-BLOB-tiedostosta.

- Matriisiprosessori (MXP): Ohjelmallinen prosessori, joka sisältää kahdeksan 32-bittistä aritmetiikka-logiikkayksikköä (ALU) ja joka on suunniteltu suorittamaan rinnakkaisoperaatioita datavektoreilla käyttäen elementtikohtaisia tensorioperaatioita, mukaan lukien yhteenlasku, vähennyslasku, xor-operaatio, siirto, kertolasku, pistetulo ja niin edelleen. Prosessori käyttää tarpeen mukaan yhdistettyä 8-bitin, 16-bitin ja 32-bitin tarkkuutta.

- CNN-kiihdytin: Nopeuttaa MXP-operaatioita käyttämällä kaksiulotteista MAC-funktiotaulukkoa, joka on toteutettu käyttäen matematiikkalohkoja ja joka toimii 8 bitin tarkkuudella.

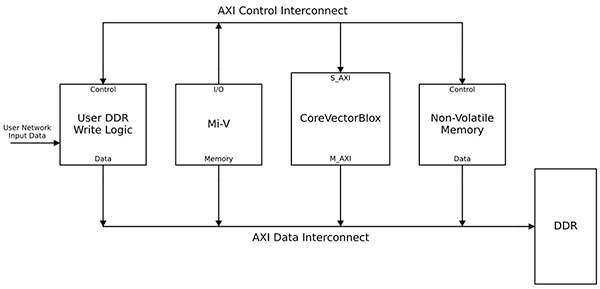

Kokonainen NN-prosessointijärjestelmä yhdistää CoreVectorBlox IP -lohkon, muistin, muistikontrollerin sekä isäntäprosessorin, esimerkkinä ohjelmallinen Microsoft RISC-V (Mi-V) -prosessoriydin (kuva 6).

Kuva 6: CoreVectorBlox IP -lohko toimii NN-päättelymallin toteuttamiseksi isäntäprosessorin kanssa, esimerkkinä Microchipin Mi-V RISC-V -mikrokontrolleri,. (Kuvan lähde: Microchip Technology)

Kuva 6: CoreVectorBlox IP -lohko toimii NN-päättelymallin toteuttamiseksi isäntäprosessorin kanssa, esimerkkinä Microchipin Mi-V RISC-V -mikrokontrolleri,. (Kuvan lähde: Microchip Technology)

Videojärjestelmätoteutuksessa isäntäprosessori lataisi laiteohjelmiston ja verkko-BLOB-tiedostot järjestelmän flash-muistista ja kopioisi ne DDR-RAM-muistiin (Double Data Rate, Random Access Memory) CoreVectorBlox-lohkon käytettäväksi. Kun isäntä prosessori ottaa vastaan videokehyksiä, se kirjoittaa ne DDR-RAM-muistiin ja ilmoittaa CoreVectorBlox-lohkolle, että tämä voi aloittaa kuvankäsittelyn. Sen jälkeen kun se on suorittanut verkko-BLOB-tiedostossa määritetyn päättelymallin, CoreVectorBlox-lohko kirjoittaa tulokset, kuvaluokitus mukaan lukien, takaisin DDR-RAM-muistiin kohdesovelluksen käytettäväksi.

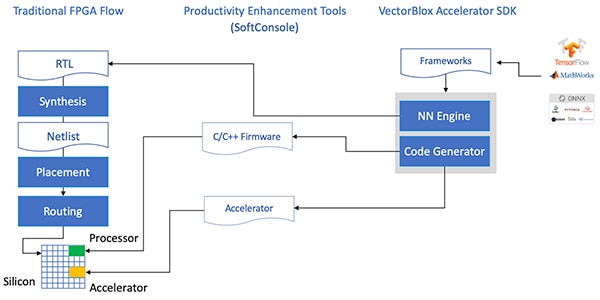

Kehitysmalli yksinkertaistaa NN-FPGA-toteutusta

Microchip suojaa kehittäjiä NN-päättelymallin toteuttamisen kompleksisuudelta PolarFire FPGA -piireillä. Sen sijaan että kehittäjien pitäisi käyttää perinteistä FPGA-mallia kaikkine yksityiskohtineen, NN-mallin kehittäjät työskentelevät tavalliseen tapaan NN-alustojensa kanssa ja lataavat saadun mallin Microchip Technologyn VectorBlox-kiihdyttimen ohjelmistokehityssarjaan (SDK). SDK generoi tarvittavat tiedostot, mukaan lukien tavallisessa FPGA-kehitysmallissa tarvittavat tiedostot, sekä aikaisemmin mainitut laiteohjelmisto- ja verkko-BLOB-tiedostot (kuva 7).

Kuva 7: VectorBlox-kiihdyttimen SDK hoitaa yksityiskohdat, joita liittyy NN-mallin toteuttamiseen FPGA-piirillä ja se generoi automaattisesti FPGA-pohjaisen päättelymallin suunnitteluun ja suorittamiseen tarvittavat tiedostot. (Kuvan lähde: Microchip Technology)

Kuva 7: VectorBlox-kiihdyttimen SDK hoitaa yksityiskohdat, joita liittyy NN-mallin toteuttamiseen FPGA-piirillä ja se generoi automaattisesti FPGA-pohjaisen päättelymallin suunnitteluun ja suorittamiseen tarvittavat tiedostot. (Kuvan lähde: Microchip Technology)

Koska VectorBlox-kiihdyttimen SDK-kehitysmalli käyttää NN-mallia FPGA-piirillä toteutetun NN-moottorin päällä, samalla FPGA-mallilla voidaan käyttää erilaisia NN-verkkoja ilman, että FPGA-mallin synteesiä tarvitsisi suorittaa uudelleen. Kehittäjät luovat C/C++ -koodin muodostettavaa järjestelmää varten ja kehittäjät voivat vaihtaa lennosta malleja järjestelmän sisällä tai suorittaa malleja samanaikaisesti aikajaotuksen avulla.

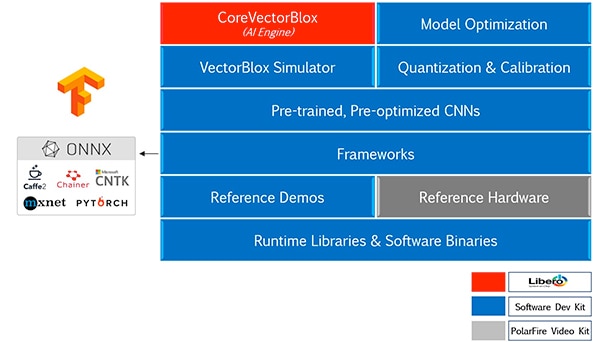

VectorBlox-kiihdyttimen SDK yhdistää Microchip Technology Libero FPGA Design Suite -ohjelmistopaketin ja kattavan joukon ominaisuuksia NN-päättelymallin kehittämiseen. SDK tarjoaa mallin optimointi-, kvantisointi- ja kalibrointipalvelun sekä NN-simulaattorin, jonka avulla kehittäjät voivat käyttää samoja BLOB-tiedostoja mallin arvioimiseen ennen kuin sitä käytetään FPGA-laitteistototeutuksessa (kuva 8).

Kuva 8: VectorBlox-kiihdyttimen SDK tarjoaa kattavan joukon palveluita, jotka on tarkoitettu optimoimaan alustassa generoitujen päättelymallien FPGA-toteutus. (Kuvan lähde: Microchip Technology)

Kuva 8: VectorBlox-kiihdyttimen SDK tarjoaa kattavan joukon palveluita, jotka on tarkoitettu optimoimaan alustassa generoitujen päättelymallien FPGA-toteutus. (Kuvan lähde: Microchip Technology)

VectorBlox-kiihdyttimen SDK tukee ONNX (Open Neural Network Exchange) -formaatin malleja samoin kuin monien muiden alustojen malleja, mukaan lukien TensorFlow, Caffe, Chainer, PyTorch ja MXNET. Tuettuja CNN-arkkitehtuureja ovat MNIST, MobileNet-versiot, ResNet-50, Tiny Yolo V2 sekä Tiny Yolo V3. Microchip tulee laajentamaan tukea sisältämään useimmat avoimen lähdekoodin kirjastossa OpenVINO toolkit open model zoo olevat verkot. Kirjasto sisältää valmiiksi koulutettuja malleja, mukaan lukien Yolo V3, Yolo V4, RetinaNet sekä SSD-MobileNet sekä muita.

Videosarja esittelee FPGA-päättelyä

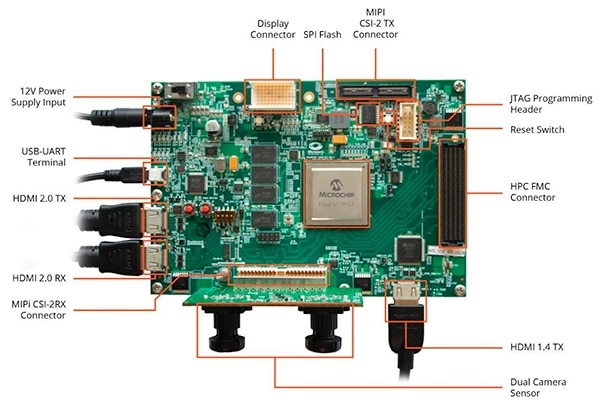

Jotta kehittäjät voisivat aloittaa nopeasti älykkäiden sulautettujen näkösovellusten kehityksen, Microchip Technology tarjoaa kattavan esimerkkisovelluksen, joka on suunniteltu käytettäväksi yrityksen MPF300-VIDEO-KIT PolarFire FPGA -video ja kuvantamissarjassa sekä referenssisuunnitelmassa.

Sarja perustuu Microchip MPF300T PolarFire FPGA -piiriin ja sen kortilla on kaksi kamerakennoa, DDR4 (Double Data Rate 4) RAM -muisti, flash-muisti, tehonhallinta sekä lukuisia rajapintoja (kuva 9).

Kuva 9: MPF300-VIDEO-KIT PolarFire FPGA -video ja kuvantamissarja sekä sen mukana tuleva ohjelmisto tarjoaa kehittäjille nopean aloituksen FPGA-pohjaiseen päättelyyn älykkäiden sulautettujen näkösovelluksien kanssa. (Kuvan lähde: Microchip Technology)

Kuva 9: MPF300-VIDEO-KIT PolarFire FPGA -video ja kuvantamissarja sekä sen mukana tuleva ohjelmisto tarjoaa kehittäjille nopean aloituksen FPGA-pohjaiseen päättelyyn älykkäiden sulautettujen näkösovelluksien kanssa. (Kuvan lähde: Microchip Technology)

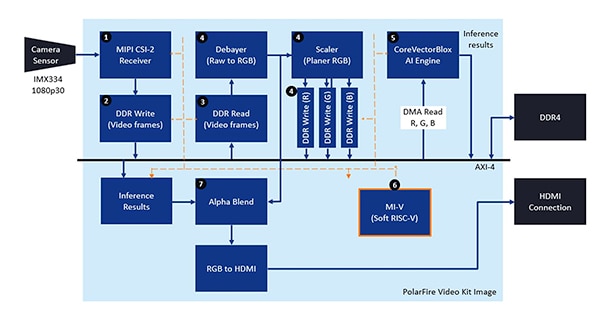

Sarjan mukana tulee kokonainen Libero-projekti, jota käytetään laiteohjelmisto- ja verkko-BLOB-tiedostojen generoimiseen. Sen jälkeen kun BLOB-tiedostot on kirjoitettu kortilla olevaan flash-muistiin, kehittäjät napsauttavat Run-painiketta Liberossa demonstraation aloittamiseksi. Tämä prosessoi kamerakennolta saatavia videokuvia ja esittää päättelyn tulokset näytöllä (kuva 10).

Kuva 10: Microchip Technology PolarFire FPGA -video- ja kuvantamissarja esittelee miten suunnitella Microchip CoreVectorBlox NN-moottorin ympärille älykkään sulautetun näköjärjestelmän FPGA-toteutus ja miten käyttää sitä. (Kuvan lähde: Microchip Technology)

Kuva 10: Microchip Technology PolarFire FPGA -video- ja kuvantamissarja esittelee miten suunnitella Microchip CoreVectorBlox NN-moottorin ympärille älykkään sulautetun näköjärjestelmän FPGA-toteutus ja miten käyttää sitä. (Kuvan lähde: Microchip Technology)

Jokaista tulon videokehystä kohti FPGA-pohjainen järjestelmä suorittaa seuraavat askeleet (askeleiden numerot vastaavat kuvaa 10):

- Lataa kehys kamerasta

- Tallenna kehys RAM-muistiin

- Lue kehys RAM-muistista

- Muunna raakakuva RGB-muotoon, muokkaa RGB-kuvaa ja tallenna tulos RAM-muistiin

- Ohjelmallinen Mi-V RISC-V -prosessori käynnistää CoreVectorBlox-moottorin, joka hakee kuvan RAM-muistista, suorittaa päättelyn ja tallentaa luokittelun todennäköisyystulokset takaisin RAM-muistiin

- Mi-V käyttää tuloksia ja luo peittokuvan, joka esittää reunaruudun, luokittelun tulokset sekä muita metatietoja ja tallentaa kehyksen RAM-muistiin

- Alkuperäinen kehys yhdistetään peittokuvakehyksen kanssa ja kirjoitetaan HDMI-näytölle.

Demonstraatio tukee Tiny Yolo V3- ja MobileNet V2 -mallien kiihdytystä, mutta kehittäjät voivat käyttää myös muita SDK:n tukemia malleja käyttäen aikaisemmin kuvattuja menetelmiä tekemällä pienen muutoksen koodiin mallin nimen ja metadatan lisäämiseksi valmiiseen listaan, joka sisältää kaksi oletusarvoista mallia.

Yhteenveto

AI-algoritmit kuten NN-mallit tarkoittavat tyypillisesti laskentaintensiivisiä työkuormia ja vaativat enemmän laskentaresursseja kuin mihin yleiskäyttöiset prosessorit pystyvät. Vaikka FPGA-piirit täyttävät hienosti suorituskykyä ja vähävirtaisuutta koskevat vaatimukset päättelymallien suorituksessa, perinteiset FPGA-kehitysmenetelmät saattavat näyttää kompleksisilta ja tästä syystä kehittäjät usein kääntyvät ei-optimaalisten ratkaisuiden puoleen.

Kuten artikkelissa osoitetaan, Microchip Technologyn erityisen IP:n ja ohjelmiston avulla myös kehittäjät, joilla ei ole kokemusta FPGA-piireistä, voivat toteuttaa päättelypohjaisia malleja, jotka täyttävät paremmin suorituskyky-, virrankulutus- samoin kuin suunnitteluaikatauluvaatimukset.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.