Täytä erilaiset toiminnalliset vaatimukset ja turvallisuusvaatimukset moniydinprosessoreilla

Julkaisija DigiKeyn kirjoittajat Pohjois-Amerikassa

2020-10-01

Autoteollisuuden, teollisuuden, robotiikan, rakennusautomaation ja muiden kriittisten sulautettujen järjestelmien ja sovellusten odotetaan pystyvän käsittelemään mitä erilaisempia kuormia aina pienitehoisesta reaaliaikaisesta seurannasta korkeatasoisiin multimediasovelluksiin, joissa käytetään monen näytön grafiikkanäyttöjä ihmisen ja koneen rajapinnoissa (HMI). Näiden laajojen toiminnallisien vaatimuksien täyttämisen lisäksi suunnittelijoiden on myös tuettava tiukkoja turvallisuusstandardeja, alentaa kustannuksia ja kokoa sekä optimoida teho/suorituskyky-tasapaino.

Näiden usein ristiriitaisten vaatimusten täyttämiseksi kehittäjien on tähän mennessä täytynyt joko uhrata toiminnallisia valmiuksia tai monimutkaistaa tuotetta ja valmistusta lisäämällä laitteita, joita tarvitaan haluttaessa tukea muun muassa grafiikkaa, tietoturvaa ja turvallisuutta koskevia erityisvaatimuksia. Kehittäjät todella tarvitsevat yhden ratkaisun, joka tukee laajaa valikoimaa erilaisia tuotteita, jotka täyttävät nämä vaatimukset erilaisissa kriittisissä sulautettujen järjestelmien sovelluksissa.

Tässä artikkelissa kuvataan nopeasti kriittisten sulautettujen järjestelmien suunnittelun kehitys. Tämän jälkeen artikkelissa näytetään kuinka moniytimisiä sovellusprosessoreja voidaan käyttää vastaamaan kehittäjien haasteisiin. Tässä käytetään erityisesti NXP Semiconductors-yrityksen tuotteita, jotka on kehitetty tukemaan nopeasti laajenevaa listaa erilaisia toiminnallisia vaatimuksia sekä turvallisuussertifioitujen ominaisuuksien vaatimuksia .

Sulautettujen järjestelmien suunnittelunäkökohtien kehitys

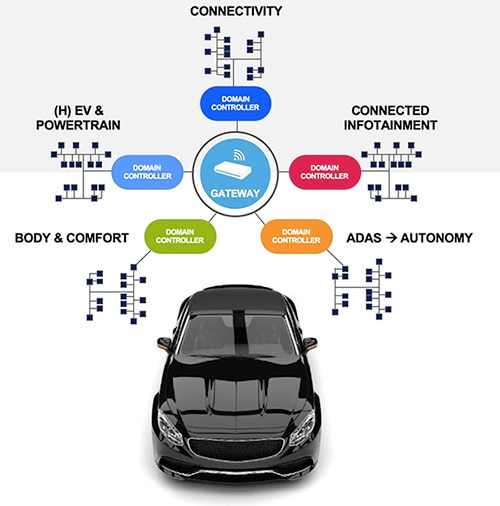

Sulautettujen laitteiden perinteinen rooli rajoitettujen järjestelmätoimintojen tukemisessa on suurelta osin korvautunut laajaa suorituskykyä tarjoavien laitteiden kysynnällä. Esimerkiksi teollisissa sovelluksissa tarve parantaa älykkäiden työkalujen ja laitteiden käyttöliittymäominaisuuksia edellyttää prosessoreilta, jotka pystyvät tarjoamaan optimoitua grafiikkaa ja täyttävät perinteiset teollisuuden reaaliaikaiset vaatimukset. Vastaavasti suuntaus autoteollisuudessa kohti hierarkkisia arkkitehtuureja, jotka muodostuvat toiminnallisista toimialueklustereista ja yhdyskäytävistä, lisää tarvetta prosessoreille, jotka pystyvät täysin vastaamaan näihin vaatimuksiin (kuva 1).

Kuva 1: Suuntaus autojärjestelmien hierarkkisempiin arkkitehtuureihin on luonut tarpeen integroituneemmille, skaalautuvammille prosessoriratkaisuille. (Kuvalähde: NXP Semiconductors)

Kuva 1: Suuntaus autojärjestelmien hierarkkisempiin arkkitehtuureihin on luonut tarpeen integroituneemmille, skaalautuvammille prosessoriratkaisuille. (Kuvalähde: NXP Semiconductors)

Kehittyneempien ominaisuuksien kysyntä jokaisella toiminnallisella alueella nostaa edelleen suorituskyvyn ja integroitujen ominaisuuksien kynnystä. Esimerkiksi heads-up-näyttöjen ilmaantuminen vaatii ratkaisuja, joilla voidaan varmistaa tärkeiden graafisten tietojen jatkuva toimittaminen kuljettajille. Näiden seuraavan sukupolven näyttöjen ohella kasvava tarve parantaa kuljettajan tietoisuutta ympäristöstään lisää vaatimuksia kamerarajapinnoille ja tehokkaille uneliaisuuden tunnistamiseen tarvittavalle korkean suorituskyvyn tunnistusohjelmistolle.

Kun sovellukset kehittyvät edelleen, erittäin integroitujen, skaalautuvien ratkaisujen tarve tulee entistä kiireellisemmäksi jotta voitaisiin vastata yhä erilaisempiin vaatimuksiin ja minimoida tuotteen koko, kustannukset ja monimutkaisuus. Käyttämällä NXP:n i.MX 8 -sovellusprosessorien tuoteperhettä kehittäjät voivat hyödyntää yhteensopivaa prosessorialustaa, joka tarjoaa runsaasti ominaisuuksia ja suorituskyvyn, jota tarvitaan erilaisten sovellusvaatimusten tukemiseen. i.MX 8 -perheen sisällä NXPi.XX 8X -sarja on tarkoitettu keskitason auto- ja teollisuussovelluksiin vaadittavien turvallisuussertifioitujen prosessorien uusiin tarpeisiin vastaamiseen.

Moniydinarkkitehtuuri hallitsee erilaiset työmäärät

Yksi vaikeuksista, joita kehittäjät kohtaavat auto- ja teollisuussovelluksien laitteiden toteuttamisessa, on yksinkertaisesti se miten valtavia vaatimukset ovat. Siinä missä kehittäjät voivat odottaa käsittelevänsä joko reaaliaikaisia tai korkean tason sovellusten käsittelyn vaatimia työkuormia, älykkäiden alijärjestelmien kysyntä on yhdistänyt nämä huomattavasti erilaiset laskentatyypit. Kehittäjät tarvitsevat yhä enemmän ratkaisuja, jotka pystyvät tarjoamaan sekä luotettavan reaaliaikaisen vasteen että sovelluksen tehokkaan suorituksen ja lisäksi tukemaan samalla toiminnallisen turvallisuuden vaatimuksia.

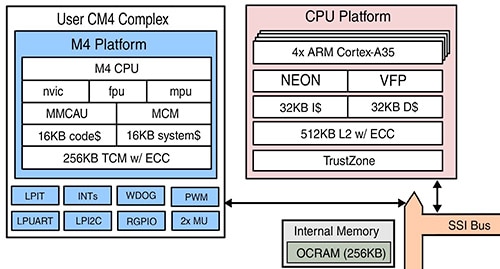

NXP i.MX 8X -sarjan prosessorit on suunniteltu tarjoamaan reaaliaikaominaisuudet, suuritehoisen prosessoinnin ja alhaisen virrankulutuksen. Niissä hyödynnetään sofistikoitunutta monen ytimen keskusyksikköarkkitehtuuria erilaisten laskennallisten työkuormien hallintaan (kuva 2).

Kuva 2: NXP i.MX 8X -sarja käyttää moniydinarkkitehtuuria, joka muodostuu sulautetusta Arm Cortex-M4 (CM4) -prosessorista ja useista Arm Cortex-A35 -sovellusprosessoreista, joita käytetään erilaisissa ohjelmistojen työkuormitustilanteissa. (Kuvalähde: NXP Semiconductors)

Kuva 2: NXP i.MX 8X -sarja käyttää moniydinarkkitehtuuria, joka muodostuu sulautetusta Arm Cortex-M4 (CM4) -prosessorista ja useista Arm Cortex-A35 -sovellusprosessoreista, joita käytetään erilaisissa ohjelmistojen työkuormitustilanteissa. (Kuvalähde: NXP Semiconductors)

i.MX 8X -laitteet sisältävät yleiskäyttöisiin reaaliaikaisiin prosessointitehtäviin Arm Cortex-M4 (CM4) -prosessorin sisältäen liukulukuyksikön (FPU), muistisuojausyksikön (MPU), muistiavaruudessa näkyvän kryptografisen kiihdytysyksikön (MMCAU) sekä erilaisia ohjausmoduuleja (MCM). Tukeakseen ulkoisia oheislaitteita, kuten antureita ja toimilaitteita, tämä käyttäjän CM4-kompleksi yhdistää sisäkkäisen vektorikeskeytysohjaimen (NVIC) kattavaan joukkoon rajapintoja ja moduuleja, mukaan lukien vähävirtainen jaksottainen keskeytysajastin (LPIT), pulssileveysmodulointi (PWM) ja muita toimintoja, joita yleisesti tarvitaan autoteollisuudessa ja teollisuudessa. Pari välimuistia ja tiukasti kytketty muisti (TCM) virheenkorjauskoodilla (ECC) auttavat minimoimaan ulkoisen muistin käytön, nopeuttavat suoritusnopeutta ja auttavat käsittelemään muistivirheet.

Sovellusten työkuormituksen nopeaa suorittamista varten mikroprosessorialusta sisältää useita virtaa säästäviä Arm Cortex-A35 -sovellusprosessoreita (AP) - kaksi AP:tä 8DualXPlus-prosessorissa, kuten MIMX8UX6AVLFZAC ja neljä AP:tä 8QuadXPlus-prosessoreissa, kuten MIMX8QX6AVLFZAC. Mikroprosessorialusta sisältää erillisen välimuistin käskyille (I$) ja datalle (D$) sekä jaetun 512 kilotavun (kt) tason 2 (L2) välimuistin ECC:llä.

Arkkitehtuurin Arm Cortex-A35 -ytimet tarjoavat sekä ohjelmistojen yhteensopivuuden että suorituskyvyn skaalautuvuuden tukemalla sekä 32-bittistä taaksepäin yhteensopivuutta että 64-bittistä suorituskykyä. Laskentaintensiivisten algoritmien, kuten signaalinkäsittelyn ja koneoppimisen, suorittamisen nopeuttamiseksi Arm Cortex-A35 -prosessorit tarjoavat vektoriliukuluku-prosessoinnin (VFP) sekä Arm Neon SIMD (Single Instruction Multiple Data) -arkkitehtuurilaajennukset. Nopeuttaakseen kuvankäsittely-, tietokonenäkö- ja koneoppimisohjelmistojen suorittamista Arm Compute Library -kirjasto tarjoaa toimintoja, jotka on optimoitu Arm-prosessorin ja -grafiikkaprosessoriyksikön (GPU) arkkitehtuureille sekä avoimen lähdekoodinNe10 C-kirjasto tarjoaa Armille optimoidut toiminnot laskentaintensiivisille toiminnoille.

Dedikoidut moottorit vähentävät primääristen mikroprosessorien kuormitusta

Käyttäjän CM4-kompleksin ja Arm Cortex-A35 -moniydinsuoritinalustan lisäksi arkkitehtuuri tarjoaa erityisiä dedikoituja moottoreita multimediasovelluksiin. Arkkitehtuuri sisältää digitaalisen signaaliprosessorin (DSP) ääni- ja äänikoodekkien käsittelyä varten sekä GPU:n ja videonkäsittely-yksikön (VPU). Laitteen GPU tukee tavallisia grafiikkakirjastoja ja nopeuttaa toimintoja käyttämällä neljää erillistä nelikomponenttista liukulukuvektoria (vec4) 16 suoritusyksiköllä ja erittäin suorituskykyisellä kaksiulotteisella blittausmoottorilla. VPU käsittelee suosittuja videoformaatteja ja nopeuttaa dekoodausta jopa 4Kp30-tarkkuuteen (progressiivinen, 30 Hz) ja koodausta 1080p30-tarkkuuteen. Piirin oma näytönohjainlohko voi puolestaan ohjata grafiikkalähdön jopa kolmeen erilliseen näyttöön.

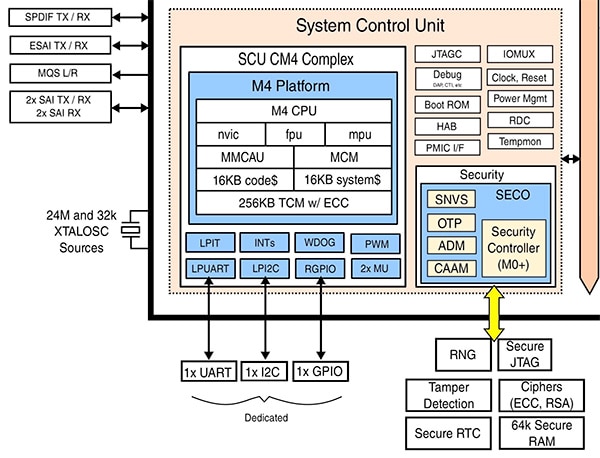

Suorituskyvyn maksimoimiseksi i.MX 8X -arkkitehtuuri sisältää lisää prosessoriytimiä, jotka on suunniteltu vapauttamaan primääriset prosessorialustat ylimääräiseltä työkuormalta, joka tyypillisesti syntyy järjestelmänhallinta- ja tietoturvapalveluiden suorittamisesta. Arkkitehtuurin järjestelmäohjausyksikkö (SCU) sisältää järjestelmän hallintaa varten CM4-kompleksin, joka vastaa käyttäjän CM4-kompleksia, mutta on täysin dedikoitu SCU-operaatioille eikä ole kehittäjien käytettävissä (kuva 3).

Kuva 3: NXP i.MX 8X -prosessoreihin syvälle integroitu SCU ei ole kehittäjien käytettävissä. SCU käyttää dedikoitua Arm Cortex-M4 (CM4) -alijärjestelmää vähentääkseen järjestelmänhallintatehtävistä syntyvää kuormitusta laitteen pääprosessoreista. (Kuvalähde: NXP Semiconductors)

Kuva 3: NXP i.MX 8X -prosessoreihin syvälle integroitu SCU ei ole kehittäjien käytettävissä. SCU käyttää dedikoitua Arm Cortex-M4 (CM4) -alijärjestelmää vähentääkseen järjestelmänhallintatehtävistä syntyvää kuormitusta laitteen pääprosessoreista. (Kuvalähde: NXP Semiconductors)

Yhdessä virranhallinnan, kellon ja muiden sisäisten toimintojen hallinnan kanssa SCU ohjaa nastojen multipleksointia sekä tulo/lähtö (I / O) -kanavan voimakkuutta normaalikäytössä. Itse asiassa käyttäjän CM4-kompleksit ja Arm Cortex-A35 AP -prosessorit eivät voi suoraan käyttää näitä erilaisia matalan tason laitteisto-ominaisuuksia. Sen sijaan SCU tarjoaa nämä ominaisuudet abstraktoimalla ne, joten käyttäjän CM4:llä tai AP:llä toimivien ohjelmistojen on yksinkertaisesti kutsuttava SCU-laiteohjelmiston ohjelmointirajapinnan (API) toimintoja suorittamaan sellaisia toimintoja kuten tarpeettomien tehoalueiden sammuttaminen. Jos kyseinen tehoalue on esimerkiksi jaettu toisen prosessorin kanssa, SCU yksinkertaisesti kuittaa virrankatkaisupyynnön, mutta pitää alueen päällä, kunnes myös kyseinen toinen prosessori lähettää virrankatkaisupyynnön.

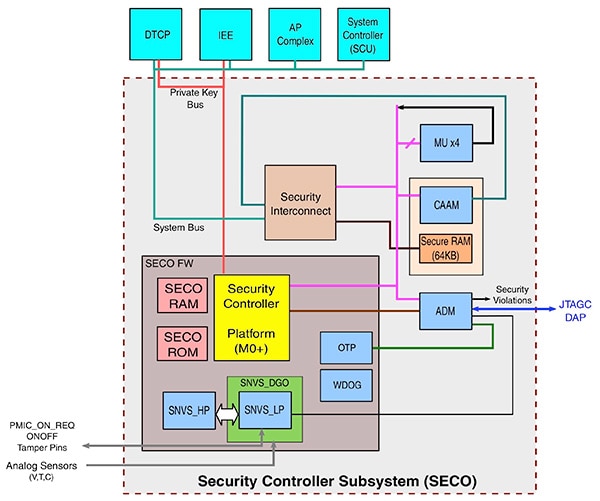

Laitteen tietoturvaohjaimen (SECO) alijärjestelmässä käytetään toista dedikoitua prosessoria i.MX 8X -laitteen kattavan tietoturvatuen hallitsemiseksi. SECO-alijärjestelmään integroitu vähävirtainen Arm Cortex-M0+ -prosessori suorittaa laiteohjelmistoa, joka tukee laitteistopohjaisia tietoturvaominaisuuksia, mukaan lukien yksityisen väylän käyttö suojattuja avaimia varten, kertaalleen ohjelmoitava (OTP) muisti avainten turvalliseen tallentamiseen sekä suojattu ei-haihtuva tallennus (SNVS) muita yksityisiä tietoja tai lyhytaikaisia avaimia varten (kuva 4).

Kuva 4: NXP i.MX 8X -tietoturvaohjaimen (SECO) alijärjestelmässä dedikoitu vähävirtainen Arm Cortex-M0+ -prosessori hallitsee tietoturvaoperaatioita hyödyntämällä omaa väylää avaimia varten ja useita laitteistomoduuleja turvallista tallennusta, krytografista kiihdytystä ja valtuutettua virheenkorjausta varten. (Kuvalähde: NXP Semiconductors)

Kuva 4: NXP i.MX 8X -tietoturvaohjaimen (SECO) alijärjestelmässä dedikoitu vähävirtainen Arm Cortex-M0+ -prosessori hallitsee tietoturvaoperaatioita hyödyntämällä omaa väylää avaimia varten ja useita laitteistomoduuleja turvallista tallennusta, krytografista kiihdytystä ja valtuutettua virheenkorjausta varten. (Kuvalähde: NXP Semiconductors)

Näiden keskeisten tietoturvamekanismien lisäksi SECO-alijärjestelmä koordinoi tietoturvaoperaatioita peukaloinnin havaitsemiseksi ja turvallisen virheenkorjauksen mahdollistamiseksi piirin ADM-moduulin (Authenticated Debug Module) kautta. Käytön suojaamiseksi laitteeseen on integrotu CAAM-moduuli (Cryptographic Acceleration and Assurance Module), joka tukee kattavasti tietoturva-algoritmeja, mukaan lukien symmetrinen ja epäsymmetrinen salaus, hajautustoiminnot ja satunnaislukugeneraattori (RNG).

Normaalissa käytössä laitteen käsittely-yksiköt, mukaan lukien SCU, AP:t ja DTCP-kiihdytin (Digital Transport Content Protection), käyttävät SECO:n suojattua liitäntää käyttääkseen CAAM-toimintoja järjestelmäväylän kautta. SECO:n dedikoitua Cortex-M0+ -prosessoria ei voi käyttää järjestelmäväylän kautta vaan ainoastaan CAAM DMA (Direct Memory Access) -toiminnon kautta. Sen sijaan se käyttää suojattuja sisäisiä yhteyksiä oheislaitteiden, suojatun RAM (Random Access Memory) -muistin, ROM (Read-Only Memory) -muistin sekä oman erityisen yksityisille avaimille varatun väylän käyttämiseen.

DTCP-kiihdyttimen käytön lisäksi tällä yksityisen avaimen väylällä on keskeinen rooli i.MX 8X -prosessorin tuessa ajonaikaiseen salaukseen ja salauksen purkamiseen. Tässä tietoturvaprosessori käyttää resurssejaan tarjotakseen laitteen IEE (Inline Encryption/Decryption Engine) -moduulin tarvitsemat yksityiset avaimet, kun se lukee turvallisesti salatusta tallennusvälineestä tai kirjoittaa siihen, ilman pyynnön esittävän prosessorin, DMA-ohjaimen tai I/O-laitteen osallistumista.

Laitteen Cortex-A35-prosessorien sisältämän Arm TrustZone -tekniikan avulla SECO-alijärjestelmä käyttää myös SCU:ta suojatun käynnistysprosessin aikana. Tässä prosessissa SCU tulkitsee käynnistysasetukset, määrittää käynnistyslähteet ja lataa käynnistyskuvat sisäiseen tai ulkoiseen muistiin. SECO-alijärjestelmä puolestaan käyttää salaustoimintoja todentaakseen allekirjoitetut laiteohjelmakuvat niiden lataamisen jälkeen, mutta ennen niiden suorittamista.

Kriittisten näyttöjen ja ohjaustoimintojen turvaaminen

Vaikka kyky käsitellä erilaisia työmääriä tehokkaasti ja turvallisesti on tärkeää, tehtäväkriittisissä sovelluksissa, kuten auto- ja teollisuussegmentit, kyky turvata keskeiset ominaisuudet ovat yhtä tärkeitä. NXP:n i.MX 8X -perhe yhdistää laitteen prosessointikyvyn turvallisuussertifioituihin ominaisuuksiin, joita tarvitaan näiden kriittisten vaatimusten täyttämiseksi.

Suoritinperheen tietoturvatuki on toteutettu useilla tasoilla, alkaen FD-SOI-prosessitekniikkaa (Fully Depleted Silicon On Insulator) käyttävästä valmistuksesta, joka parantaa järjestelmän luotettavuutta. Koska järjestelmän turvallisuus riippuu robustista tietoturvaperustasta, TrustZone-yhteensopivien AP:iden, SECO-alijärjestelmän ja suojatun käynnistyksen yhdistelmä voi tarjota sellaisen luotettavan ympäristön, jota tarvitaan turvallisuuteen kohdistuvien uhkien estämiseksi.

Samalla mahdollisuus hoitaa aikakriittisiä tehtäviä itsenäisesti käyttäjän CM4-kompleksin kanssa ja antaa kriittiset järjestelmätehtävät SCU- ja SECO-alijärjestelmille auttaa varmistamaan, että tehtäväkriittiset sovellusominaisuudet ovat käytettävissä vaihtelevasta työkuormituksesta huolimatta. Itse asiassa NXP laajentaa tätä konseptia tukemalla toimintakriittisiä näyttöjä yrityksen SafeAssure-tekniikan avulla, joka lisää i.MX 8X -laitteisiin ASIL B (Automotive Safety Integrity Level B) -valmiin laitteiston näytön vikatilanteita varten. SafeAssuren avulla käyttäjille toimitetaan automaattisesti vikaturvallinen kuva, jos laite havaitsee virheen tietojen eheydessä tai GPU-virheen. Tämä taustalla toimiva vikaturvallinen kuva varmistaa, että kriittiset tiedot ovat käytettävissä myös ensisijaisen näytön vikatilanteessa.

Tietoturvasovellusten tuki kattaa muistin käytön i.MX 8X -järjestelmissä. Tuettujen muistiliitäntöjen joukossa i.MX 8X -laitteet tarjoavat 8-bittisen ECC:n DDR3L (Double Data Rate 3 Low voltage) -muisteille. Yhdessä L2-välimuistin ECC:n kanssa (katso kuva 2 uudelleen) tämä DDR3L ECC -ominaisuus tukee teollisuuden SIL 3 -tasoa (Safety Integrity Level 3). i.MX 8X -arkkitehtuuri laajentaa ECC-tuen myös ulkoisiin flash-tallennuslaitteisiin. Tässä integroitu Bose-, Ray-Chaudhuri-, Hocquenghem (BCH) -kooderi- ja dekooderimoduuli tarjoaa 62-bittisen ECC:n, joka kykenee korjaamaan 2–20 yhden bitin virhettä näiltä tallennuslaitteilta luetun tietolohkon sisällä.

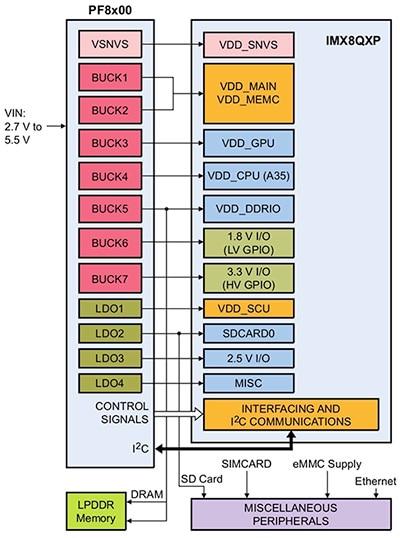

i.MX 8X -pohjaisten sovellusten käynnistäminen

Kuten minkä tahansa tämän luokan prosessorin kohdalla, i.MX 8X -pohjaisen tuotteen toteuttaminen vaatii tarkkaa huomiota tiukkoihin virransäästövaatimuksiin, mukaan lukien kriittiset käynnistyssekvenssit. i.MX 8X -laitteiden käynnistäminen edellyttää neljän eri tehoryhmän peräkkäistä tai samanaikaista käynnistystä alkaen SVNS-alijärjestelmästä ja jatkamalla SCU:lla, I/O-laitteilla ja muistirajapinnoilla ja lopuksi laitteen jäljellä olevilla toiminnoilla. Kehittäjät voivat täyttää tämän vaatimuksen yksinkertaisesti käyttämällä NXP:n PF8x00 PMIC (Power Management Integrated Circuit) -laitteita, jotka tarjoavat kattavan joukon jännitekiskoja ja ohjaussignaaleja, joita tarvitaan i.MX 8X -prosessorien, ulkoisen muistin ja tyypillisten järjestelmän oheislaitteiden tukemiseen (kuva 5) .

Kuva 5: NXP PF8x00 PMIC -laitteet tarjoavat kattavan joukon i.MX 8X -prosessorien tarvitsemia jännitekiskoja ja ohjaussignaaleja. (Kuvalähde: NXP Semiconductors)

Kuva 5: NXP PF8x00 PMIC -laitteet tarjoavat kattavan joukon i.MX 8X -prosessorien tarvitsemia jännitekiskoja ja ohjaussignaaleja. (Kuvalähde: NXP Semiconductors)

Toteuttaessaan omia i.MX 8X-pohjaisia tuotteitaan kehittäjät voivat käyttää NXP:n MC33PF8100CCES-PMIC-piiriä, joka on esiohjelmoitu käytettäväksi 8QuadXPlus-prosessorien, kuten MIMX8QX6AVLFZAC:n, kanssa. Muut PF8x00-vaihtoehdot, kuten MC33PF8100A0ES ja MC33PF8200A0ES, tukevat i.MX 8X -suorittimia, mutta niitä ei ole esiohjelmoitu.

PF8200-sarjan laitteet, kuten MC33PF8200A0ES, sisältävät turvallisuussovelluksia varten ominaisuuksia, jotka on suunniteltu tukemaan ASIL B -järjestelmiä. Useiden sisäisten tarkkailulaitteiden lisäksi, mukaan lukien omaa dedikoitua referenssivaihteluvälilä käyttävä lähtöjännitteen seuranta, PF8200 PMIC -laitteet sisältävät vikaturvallisen lähtönastan (FSOB), jonka tarkoitus on pitää järjestelmä turvallisessa tilassa käynnistyksen ja sähkökatkon aikana. Lisäksi ABIST (Analog Built In Self-Test) -rutiini testaa kaikki jännitemittarit, kun taas itsetestausrutiini varmistaa laitteen muut toiminnot.

Vaikka PF8x00 PMIC -laitteet voivat yksinkertaistaa i.MX 8X-pohjaisten järjestelmien laitteistosuunnittelua, joidenkin kehittäjien on ehkä välittömästi aloitettava i.MX 8X -laitteiden arviointi ja kokeilla nopeita prototyyppejä i.MX 8X-pohjaisista sovelluksista. NXP:n MCIMX8QXP-CPU i.MX 8X Multisensory Enablement Kit (MEK) tarjoaa valmiin kehitysalustan, joka yhdistää NXP i.MX 8QuadXPlus -prosessorin, NXP F8100 PMIC:n, 3 gigatavua (Gt) RAM-muistia, 32 Gt eMMC-muistia (Embedded Multi-Media Controller) ja 64 megatavuna (Mt) flash-muistia. Näyttö-, kamera- ja ääniliitäntöjen lisäksi MEK-kortti sisältää joukon antureita, joita käytetään tyypillisesti auto- tai teollisuussovelluksissa. Halutessaan lisää yhteys-, ääni- ja laajennusvaihtoehtoja kehittäjät voivat myös käyttää NXP:n MCIMX8-8X-BB-lisäkorttia.

Yhteenveto

Yhä useamman sovelluksen työkuormitus on laajentunut esimerkiksi autoteollisuudessa, teollisuudessa, rakennusautomaatiossa ja käyttöliittymissä vaatimaan sekä perinteisestä reaaliaikaista I/O-käsittelyä että kasvavaa sovellustason prosessointia sisältäen multimediagrafiikka. Vaikka jokaiselle työkuormalle on tarjolla suunnitteluvaihtoehtoja, on vain harvoja ratkaisuita, jotka vastaavat kasvaviin vaatimuksiin koskien korkeaa suorituskykyä ja energiatehokkaita ratkaisuita ja jotka pystyvät täyttämään turvallisuussertifioitujen tuotteiden vaatimukset autoteollisuudessa ja teollisuudessa.

Kuten tässä artikkelissa on osoitettu, kehittäjät voivat moniytimisen NXP Semiconductors -prosessoriperheen avulla toteuttaa tehokkaammin tuotteita, jotka pystyvät vastaamaan näihin erilaisiin vaatimuksiin ja skaalautumaan helposti kasvaviin suorituskykyvaatimuksiin vastaamiseksi.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.