FPGA SoC ‑piirien käyttö turvallisten ja verkkoon kytkettyjen kovien reaaliaikaisten järjestelmien kehittämisessä

Julkaisija DigiKeyn kirjoittajat Pohjois-Amerikassa

2023-02-16

Ohjelmoitavat porttimatriisit (FPGA), Linux-yhteensopivat RISC-V-mikrokontrollerialijärjestelmät (MCU), edistyneet muistiarkkitehtuurit ja suorituskykyiset viestintärajapinnat ovat tärkeitä työkaluja suunnittelijoille. Tämä pätee erityisesti suunniteltaessa turvallisia verkkoon kytkettyjä järjestelmiä, turvallisuuskriittisiä järjestelmiä ja erilaisia kovia reaaliaikaisia deterministisiä järjestelmiä, kuten tekoäly (AI) ja koneoppiminen (ML).

Näiden moninaisten elementtien integroiminen turvalliseksi, verkkoon kytketyksi ja deterministiseksi järjestelmäksi voi kuitenkin olla haastavaa ja viedä paljon aikaa, samoin kuin erilaisten järjestelmäelementtien välisten nopeiden liitäntöjen suunnittelu. Tarvitaan muistinhallintayksikkö, muistinsuojausyksikkö, tuki suojatulle käynnistykselle ja gigabittiluokan lähetin-vastaanottimet nopeita yhteyksiä varten. Tarvitaan myös aktiivista ja staattista tehonhallintaa sekä kytkentäsysäysvirtojen hallintaa. Joidenkin ratkaisuiden on toimittava laajennetulla kaupallisella lämpötila-alueella 0–100 °C:n liitoslämpötilassa (TJ), kun taas teollisuusympäristöissä käytettävien järjestelmien on toimittava −40...+100 °C:n TJ-lämpötilassa.

Näiden ja muiden haasteiden ratkaisemiseksi suunnittelijat voivat älykkäitä, yhdistettyjä ja deterministisiä järjestelmiä suunnitellessaan käyttää FPGA-järjestelmäpiirejä (SoC), joissa yhdistyvät alhainen virrankulutus, lämpötehokkuus sekä sotilastason suojaus.

Tässä artikkelissa luodaan katsaus tällaisen FPGA SoC ‑järjestelmän arkkitehtuuriin ja siihen, miten se tukee verkkoon kytkettyjen ja determinististen järjestelmien tehokasta suunnittelua. Sen jälkeen artikkelissa esitellään lyhyesti EEMBC CoreMark-Pro ‑prosessointitehon ja virrankulutuksen suorituskykytestien vertailu sekä tyypillisen FPGA SoC-piirin suorituskykytestin tulokset. Artikkelissa tarkastellaan, miten tietoturva sisältyy olennaisesti näihin FPGA SoC ‑piireihin ja esitellään esimerkkeinä Microchip Technologyn FPGA SoC ‑piirejä ja suunnitteluprosessia nopeuttava kehitysalusta. Artikkelin lopussa esitetään lyhyt luettelo MikroElektronikan laajennuskorteista, joita voidaan käyttää erilaisten viestintärajapintojen sekä maailmanlaajuisen satelliittipaikannuksen (GNSS) toteuttamiseen.

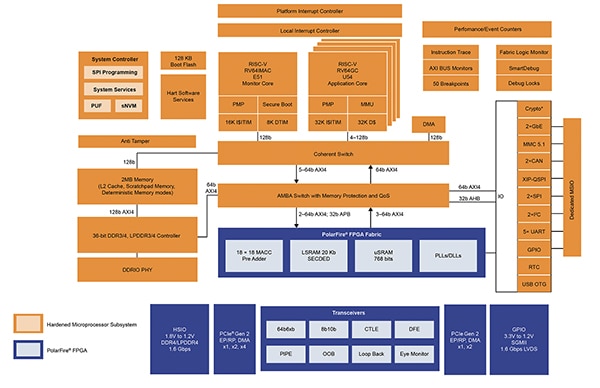

FPGA-alustaa käyttävät SoC-järjestelmäpiirit

Tämän SoC:n ”siruna” käytetään FPGA-alustaa, joka sisältää järjestelmän elementit FPGA:sta RISC-V MCU ‑alijärjestelmään, joka on toteutettu kovetetulla FPGA-logiikalla. MCU-alijärjestelmä sisältää neliytimisen RISC-V MCU ‑klusterin, RISC-V-valvontaytimen, järjestelmäohjaimen ja deterministisen L2-muistialijärjestelmän. Näiden SoC-järjestelmäpiirien FPGA sisältää jopa 460 000 logiikkaelementtiä, nopeudeltaan jopa 12,7 Gbps:n lähetin-vastaanottimen ja muita I/O-lohkoja, mukaan lukien GPIO- ja PCIe 2 ‑liitännät. Kokonaisarkkitehtuuri on suunniteltu luotettavuutta silmälläpitäen. Se sisältää yhden virheen korjauksen ja kahden virheen tunnistuksen (SECDED) kaikissa muisteissa, differentiaalisen tehoanalyysin (DPA), fyysisen muistin suojauksen ja 128 kilobittiä flash-käynnistysmuistia (kuva 1).

Kuva 1: Kaikki tämän FPGA SoC-piirin elementit, RISC-V-alijärjestelmät mukaan lukien, on toteutettu FPGA-rakenteessa. (Kuvan lähde: Microchip Technology)

Kuva 1: Kaikki tämän FPGA SoC-piirin elementit, RISC-V-alijärjestelmät mukaan lukien, on toteutettu FPGA-rakenteessa. (Kuvan lähde: Microchip Technology)

Microchip tarjoaa kolmannen osapuolen työkaluja ja suunnitteluresursseja sisältävän Mi-V-ekosysteeminsä (lausutaan ”my five”) tukemaan RISC-V-järjestelmien toteutusta. Se on suunniteltu nopeuttamaan RISC-V-käskykanta-arkkitehtuurin (ISA) käyttöönottoa kovetetuissa RISC-V-ytimissä ja ohjelmallisissa RISC-V-ytimissä. Mi-V-ekosysteemin elementteihin sisältyy:

- immateriaaliomaisuuden (IP) lisenssit

- laitteisto

- käyttöjärjestelmät ja väliohjelmistot

- debuggerit, kääntäjät ja suunnittelupalvelut.

FPGA SoC-piirin kovetetut RISC-V-mikrokontrollerit sisältävät useita virheenetsintäominaisuuksia, kuten passiivinen ajonaikana konfiguroitava AXI-väylä sekä käskyjen jäljitys. AXI:n avulla voidaan valvoa erilaisiin muisteihin kirjoitettavia tai niistä luettavia tietoja ja tietää, milloin niitä kirjoitetaan tai luetaan.

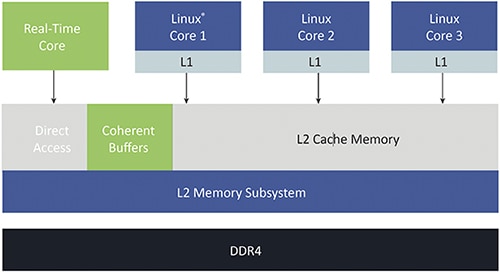

RISC-V MCU ‑alijärjestelmä käyttää viisiportaista yhden käskyn kerrallaan suorittavaa kiinteästi ajoitettua liukuhihnaa. Se ei ole haavoittuvainen Spectre- tai Meltdown-hyväksikäyttömenetelmille, jotka voivat vaikuttaa dynaamista ajoitusta käyttäviin arkkitehtuureihin. Kaikki viisi mikrokontrolleria käyttävät samaa muistialijärjestelmää ja tukevat erilaisia deterministisiä epäsymmetristä moniprosessointia (AMP) käyttäviä reaaliaikaisia järjestelmiä sekä Linuxia. RISC-V-alijärjestelmän ominaisuuksia ovat muun muassa (kuva 2):

- Linuxin suoritus ja kovat reaaliaikaiset toiminnot

- L1- ja L2-muistien määrittely deterministiseksi muistiksi

- DDR4-muistialijärjestelmä

- Haarautumisen ennakoinnin käyttöönotto / käytöstä poisto

- Kiinteästi ajoitettu liukuhihna

Kuva 2: RISC-V-alijärjestelmä sisältää useita suoritin- ja muistielementtejä. (Kuvan lähde: Microchip Technology)

Kuva 2: RISC-V-alijärjestelmä sisältää useita suoritin- ja muistielementtejä. (Kuvan lähde: Microchip Technology)

Enemmän prosessointia pienemmällä energiankulutuksella

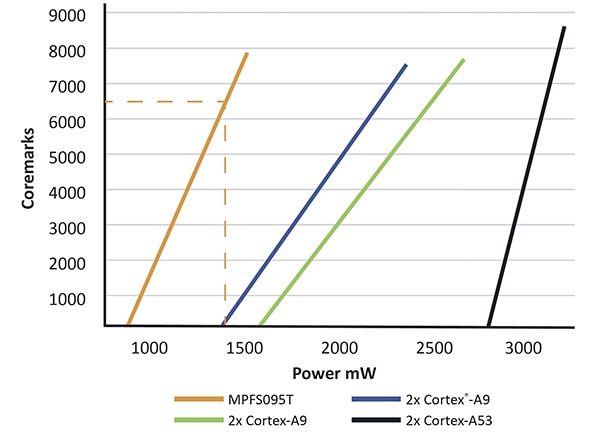

Järjestelmän toiminnallisten etujen, kuten kovan reaaliaikaisen prosessointituen, lisäksi nämä FPGA SoC ‑järjestelmät ovat erittäin energiatehokkaita. EEMBC CoreMark-PRO ‑suorituskykytesti on alan standardi mikrokontrollerien tehokkuuden ja suorituskyvyn vertailemisessa sulautetuissa järjestelmissä. Se suunniteltiin erityisesti mittaamaan laitteiston suorituskykyä ja korvaamaan Dhrystone-suorituskykytesti.

CoreMark-PRO-työkuormiin sisältyy erilaisia suorituskykyominaisuuksia, käskytason rinnakkaisuutta ja muistin käyttöä neljän liukulukutyökuorman ja viiden tavanomaisen kokonaislukutyökuorman perusteella. Liukulukutyökuormat sisältävät LINPACK-kirjastosta johdetun lineaarisen algebrarutiinin, nopean Fourier-muunnoksen, neuroverkkoalgoritmin kuvioiden arviointia varten sekä parannellun version Livermore loops ‑suorituskykytestistä. JPEG-pakkaus, XML-jäsennin, ZIP-pakkaus ja 256-bittinen suojattu hajautusalgoritmi (SHA-256) muodostavat kokonaislukutyökuormien perustan.

Näiden FPGA SoC ‑piirien MPFSO95T-mallit, kuten MPFS095TL-FCSG536E, saavuttavat jopa 6 500 Coremark-pistettä 1,3 watin teholla (kuva 3).

Kuva 3: MPFS095T FPGA SoC (oranssi viiva) saavuttaa 6 500 Coremark-pistettä 1,3 watin teholla. (Kuvan lähde: Microchip Technology)

Kuva 3: MPFS095T FPGA SoC (oranssi viiva) saavuttaa 6 500 Coremark-pistettä 1,3 watin teholla. (Kuvan lähde: Microchip Technology)

Turvallisuusnäkökohtia

Näiden FPGA-SoC-piirien turvallisuuskriittiset ja kovat reaaliaikaiset sovellukset vaativat vahvaa turvallisuutta korkean energiatehokkuuden ja tehokkaan prosessointikyvyn lisäksi. Näiden FPGA-SoC-piirien perusturvatoimintoja ovat differentiaaliselle tehoanalyysille (DPA) vastustuskykyinen bittivirtaohjelmointi, todellinen satunnaislukugeneraattori (TRNG) ja fyysisesti kloonaamaton toiminto (PUF). Ne sisältävät myös tavallisen ja käyttäjän määrittämän turvallisen käynnistyksen, fyysisen muistin suojauksen, joka tarjoaa koneen etuoikeustilaan liittyviä pääsyrajoituksia muistiin, mukaan lukien kone-, ohjaus- tai käyttäjätilat, sekä immuniteetin Meltdown- ja Spectre-hyökkäyksille.

Turvallisuus alkaa suojatusta toimitusketjun hallinnasta, mukaan lukien laitteistoturvamoduulien (HSM) käyttö puolijohdekiekkojen testauksen ja pakkaamisen aikana. Jokaiseen FPGA SoC ‑piiriin sulautetun 768 tavun digitaalisesti allekirjoitetun x.509 FPGA ‑varmenteen käyttö lisää toimitusketjun varmuutta.

Näissä FPGA SoC ‑piireissä on lukuisia siruun rakennettuja ilmaisimia väärinkäyttöä vastaan, jotka takaavat turvallisen ja luotettavan toiminnan. Jos väärinkäyttöä havaitaan, aktivoituu väärinkäyttölippu, jonka avulla järjestelmä voi reagoida tarpeen mukaan. Joitakin käytettävissä olevia väärinkäytön ilmaisimia ovat:

- jännitemonitorit

- lämpötila-anturit

- kellohäiriö- ja kellotaajuusilmaisimet

- JTAG aktiivinen ‑ilmaisin

- silmukka aktiivinen ‑ilmaisin.

Suojausta parantavat lisäksi vastatoimet AES-256-salausmenetelmän symmetristen lohkojen salauskorrelaation tehoanalyysihyökkäykselle (CPA), integroidut salaustiivistelmäominaisuudet, joilla varmistetaan tietojen eheys, integroitu PUF avaintallennusta varten ja FPGA-alustan ja kaikkien sirumuistien nollausmahdollisuus.

Esimerkkejä FPGA SoC ‑piireistä

Microchip Technology yhdistää nämä ominaisuudet ja teknologiat PolarFire FPGA SoC ‑piireissään, jotka tarjoavat useita eri nopeusluokkia, lämpötila-alueita ja pakkauskokoja, joiden avulla voidaan suunnitella mitä erilaisimpia ratkaisuja 25 000 – 460 000 logiikkaelementillä. Saatavana on neljä lämpötilaluokkaa (kaikissa käytetään TJ-luokitusta): laajennettu kaupallinen alue 0 ... +100 °C , teollisuusalue −40 ... +100 °C, autoteollisuusalue −40 ... +125 °C ja sotilasalue −55 ... +125 °C.

Suunnittelijat voivat käyttää tavallisen nopeusluokan laitteita tai nopeusluokan -1 laitteita, jotka ovat 15 % nopeampia. Näitä FPGA SoC ‑piirejä voidaan käyttää 1,0 voltin jännitteellä pyrittäessä minimoimaan virrankulutus tai 1,05 voltin jännitteellä suorituskyvyn parantamiseksi. Niitä on saatavana erikokoisissa pakkauksissa, mukaan lukien 11 × 11 mm, 16 × 16 mm ja 19 × 19 mm.

Käyttökohteissa, joissa vaaditaan laajennettua kaupallista toimintalämpötila-aluetta, tavallista nopeutta ja 254 000 logiikkaelementtiä 19 x 19 mm:n pakkauksessa, voidaan käyttää MPFS250T-FCVG484EES-piiriä. Yksinkertaisemmissa käyttökohteissa, joissa tarvitaan 23 000 logiikkaelementtiä, voidaan käyttää MPFS025T-FCVG484E-piiriä, joka tukee sekin laajennettua kaupallista toimintalämpötila-aluetta ja tavallista nopeutta 19 x 19 mm:n pakkauksessa. 254 000 logiikkaelementtiä sisältävä MPFS250T-1FCSG536T2 on suunniteltu suorituskykyisiin autoteollisuuden järjestelmiin. Sen toimintalämpötila-alue on −40 ... +125 °C ja nopeusluokka on -1, mikä nostaa kellotaajuutta 15 %. Laite käyttää kompaktia 16 × 16 mm:n pakkausta, jossa on 536 juotosnystyä 0,5 mm:n jaolla (kuva 4).

Kuva 4: Autoteollisuuden lämpötila-alueen MPFS250T-1FCSG536T2 käyttää 16 × 16 mm:n pakkausta, jossa on 536 juotosnystyä 0,5 mm:n jaolla. (Kuvan lähde: Microchip Technology)

Kuva 4: Autoteollisuuden lämpötila-alueen MPFS250T-1FCSG536T2 käyttää 16 × 16 mm:n pakkausta, jossa on 536 juotosnystyä 0,5 mm:n jaolla. (Kuvan lähde: Microchip Technology)

FPGA SoC ‑kehitysalusta

Microchip Technology tarjoaa PolarFire FPGA SoC ‑piiriä käyttävien järjestelmien suunnittelun nopeuttamiseksi MPFS-ICICLE-KIT-ES PolarFire SoC Icicle ‑rakennussarjan, jonka avulla voidaan kokeilla viisiytimistä Linux-yhteensopivaa RISC-V-mikroprosessorialijärjestelmää vähävirtaisella ja reaaliaikaisella suorituksella. Sarja sisältää ilmaisen Libero Silver ‑lisenssin, jota tarvitaan mallien arviointiin. Se tukee ohjelmointia ja virheenkorjausta yhdellä kielellä.

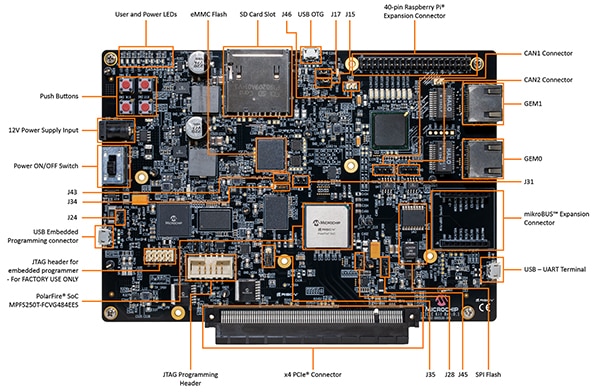

Näitä FPGA SoC ‑piirejä tukee VectorBlox kiihdytinohjelmistokehityspaketti (SDK), joka mahdollistaa vähävirtaiset, pienikokoiset tekoäly-/koneoppimissovellukset. Suunnitteluprosessin yksinkertaistamista on painotettu siinä määrin, että suunnittelijalla ei tarvitse olla aiempaa FPGA-suunnittelukokemusta. VectorBlox-kiihdytin-SDK:n avulla kehittäjät voivat ohjelmoida vähän energiaa kuluttavia neuroverkkoja käyttäen C/C++-ohjelmointikieliä. Icicle-sarjassa on lukuisia ominaisuuksia, jotka tarjoavat kattavan kehitysympäristön. Ominaisuudet sisältävät muun muassa monen jännitetason virtamittausjärjestelmän erilaisten jännitealueiden valvontaa varten, PCIe-juuriportin ja piirilevyllä olevia muisteja (mukaan lukien LPDDR4, QSPI ja eMMC Flash). Sillä voidaan ajaa käyttöjärjestelmiä Linux ja Raspberry Pi. Laitteen mikroBUS-laajennusportit tarjoavat monenlaisia langallisia ja langattomia yhteysvaihtoehtoja, sekä toiminnallisia laajennuksia, kuten GNSS-paikannus (kuva 5).

Kuva 5: Tämä kattava FPGA SoC ‑kehitysympäristö sisältää liittimet Raspberry Pi- (ylhäällä oikealla) ja mikroBUS-laajennuskorteille (oikea alakulma). (Kuvan lähde: Microchip Technology)

Kuva 5: Tämä kattava FPGA SoC ‑kehitysympäristö sisältää liittimet Raspberry Pi- (ylhäällä oikealla) ja mikroBUS-laajennuskorteille (oikea alakulma). (Kuvan lähde: Microchip Technology)

Laajennuskortit

Esimerkkejä mikroBUS-laajennuskorteista:

MIKROE-986, jolla voidaan lisätä CAN-väyläliitäntä käyttäen sarjamuotoista oheislaiteväylää (SPI)

MIKROE-1582, jolla muodostetaan yhteys mikrokontrollerin ja RS-232-väylän välille

MIKROE-989, RS422/485-tiedonsiirtoväylään liittämistä varten

MIKROE-3144, joka tukee LTE Cat M1- ja NB1-teknologioita, jotka mahdollistavat luotettavan ja helpon yhteyden 3GPP IoT ‑laitteisiin.

MIKROE-2670, joka mahdollistaa GNSS-toiminnallisuuden GPS- ja Galileo-konstellaatioiden sekä joko BeiDoun tai GLONASSin samanaikaisella vastaanotolla, mikä parantaa paikannuksen tarkkuutta signaalin ollessa heikko tai jos kaupunkialueella on paljon häiriöitä.

Yhteenveto

FPGA SoC ‑piirejä voidaan käyttää kehitettäessä verkkoon kytkettyjä, turvallisuuskriittisiä ja kovia reaaliaikaisia deterministisiä järjestelmiä. FPGA SoC ‑piirit tarjoavat laajan valikoiman järjestelmäelementtejä, kuten FPGA-alustan, RISC-V MCU ‑alijärjestelmän, jossa on suorituskykyiset muistit, nopeat tiedonsiirtoliitännät ja lukuisia turvallisuustoimintoja. Suunnittelun aloittamiseksi on saatavilla kehityspiirilevyjä ja -ympäristöjä, jotka sisältävät kaikki tarvittavat elementit, mukaan lukien laajennuskortit, joita voidaan käyttää monenlaisien viestintä- ja paikannustoimintojen toteuttamiseen.

Suositeltavaa luettavaa

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.