Miten suunnitella ja sertifioida toiminnallisesti turvallisia RTD-pohjaisia järjestelmiä

Julkaisija DigiKeyn kirjoittajat Pohjois-Amerikassa

2023-07-24

Vastuslämpötilamittari (RTD), joka koostuu anturista ja sen analogisesta etuasteen (AFE) signaalinkäsittelypiiristä, on laajalti käytetty, tarkka ja luotettava. Toiminnan kannalta kriittisissä ja korkeaa luotettavuutta vaativissa sovelluksissa on kuitenkin usein tarpeen suunnitella ja varmistaa toiminnallisesti turvallinen järjestelmä Route 1S- tai Route 2S ‑komponenttisertifiointiprosessin kautta.

Järjestelmän sertifiointi toiminnallisen turvallisuuden varmistamiseksi on monimutkainen prosessi, koska kaikki järjestelmän osat on tarkistettava mahdollisten vikatilojen ja -mekanismien varalta. Vikojen diagnosointiin on useita menetelmiä, ja jo sertifioitujen osien käyttö helpottaa tätä työmäärää sertifiointiprosessin yhteydessä.

Huomaa, että vaikka luotettavuus liittyy toiminnalliseen turvallisuuteen, se ei ole sama asia. Yksinkertaisimmillaan ”luotettava” viittaa ratkaisuun ja toteutukseen, joka toimii määritysten mukaisesti ilman ongelmia tai vikoja, kun taas ”toiminnallisesti turvallinen” tarkoittaa, että ratkaisussa on otettava huomioon kaikki viat. Kriittisissä sovelluksissa tarvitaan sekä luotettavuutta että toiminnallista turvallisuutta.

Tässä artikkelissa tarkastellaan vastuslämpötilamittarien ja niiden signaalinkäsittelypiirien perusteita toiminnallisesti turvallisen sertifioinnin kontekstissa. Sen jälkeen artikkelissa tarkastellaan erilaisia luotettavuus- ja vikasertifiointitasoja sekä sitä, mitä tarvitaan niiden täyttämiseen kummassakin sertifiointiprosessissa. Avainasioiden havainnollistamiseen käytetään kahta monikanavaista RTD AFE -piiriä (Analog Devices ‑yrityksen AD7124-pari) sekä niihin liittyvää evaluointikorttia.

Toiminnallisen turvallisuuden rooli

Toiminnallisen turvallisuuden roolina on poistaa ihmisten loukkaantumisen tai terveysvahinkojen riski toteuttamalla asianmukaisesti yksi tai useampi automaattinen suojaus-/turvallisuustoiminto. Se varmistaa, että tuote, laite tai järjestelmä toimii edelleen turvallisesti, vaikka järjestelmässä esiintyisikin toimintahäiriö. Sitä tarvitaan monenlaisissa teollisissa, kaupallisissa ja jopa joissakin kuluttajasovelluksissa, kuten seuraavissa:

- autonomiset ajoneuvot

- koneturvallisuus ja robotiikka

- teollisuuden ohjausjärjestelmät (ICS)

- kuluttajatason älykotituotteet

- älykkäät tehtaat ja toimitusketjut

- turvainstrumentoidut järjestelmät ja vaarallisten kohteiden ohjausjärjestelmät.

Esimerkki toiminnallisesti turvallisesta ratkaisusta on se, että virta voidaan edelleen katkaista päävirtakytkimellä, vaikka muut järjestelmän osat pettäisivätkin (kuva 1).

Kuva 1: Toiminnallisesti turvallisessa järjestelmässä ei voi olla epäselvyyttä siitä, tekeekö tämä kytkin sen, mihin se on suunniteltu. (Kuvan lähde: Pilla City Electric Supply Co:n kautta.)

Kuva 1: Toiminnallisesti turvallisessa järjestelmässä ei voi olla epäselvyyttä siitä, tekeekö tämä kytkin sen, mihin se on suunniteltu. (Kuvan lähde: Pilla City Electric Supply Co:n kautta.)

RTD-teknologian perusteet

Miksi tarkastella lämpötilaa ja toiminnallista turvallisuutta? Yksi hyvä syy on se, että lämpötila on yleisimmin mitattu fyysinen suure. Se liittyy usein turvallisuuteen tai kriittisiin sovelluksiin, ja sitä tukee laaja valikoima antureita. Näihin kuuluu RTD, joka on käsitteellisesti yksinkertainen: siinä hyödynnetään nikkelin, kuparin ja platinan kaltaisten metallien tunnettua ja toistettavaa vastuksen lämpötilakerrointa (TCR). Platinasta valmistettuja RTD-komponentteja, joiden vastus on 100 ohmia (Ω) ja 1000 ohmia lämpötilassa 0 °C, käytetään eniten, ja niitä voidaan käyttää lämpötiloissa −200 °C ... 850 °C.

Näiden RTD-komponenttien vastus muuttuu tällä lämpötila-alueella erittäin lineaarisesti lämpötilan mukaan. Erittäin suurta tarkkuutta vaativia tilanteita varten on korjaus- ja kompensaatiotaulukoita sekä kertoimia, joita voidaan käyttää. Platinasta valmistetun RTD-komponentin, jonka nimellisvastus on 100 Ω (eli PT100), vastus on tyypillisesti 18 Ω lämpötilassa −200 °C ja 390,4 Ω lämpötilassa +850 °C.

RTD-KOMPONENTIN käyttö edellyttää, että sen läpi syötetään tunnettu sähkövirta, yleensä noin 1 milliampeeri (mA) lämpenemisen minimoimiseksi. Myös muita virta-arvoja käytetään RTD-komponentin nimellisvastuksesta riippuen.

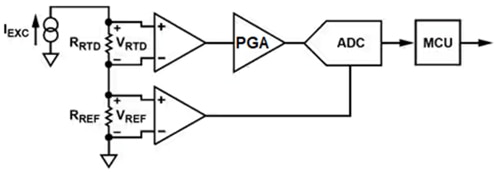

RTD-komponentin jännitehäviö mitataan samanaikaisesti AFE-asteen kautta, joka koostuu PGA-vahvistimesta ja lähes aina analogia–digitaalimuuntimesta (ADC) sekä mikrokontrollerista (MCU) (kuva 2).

Kuva 2: RTD-komponentin käyttäminen lämpötilan mittaamiseen edellyttää tunnetun virran syöttämistä RTD-komponentin läpi ja jännitehäviön mittaamista, minkä jälkeen sovelletaan Ohmin lakia. (Kuvan lähde: Digi-Key)

Kuva 2: RTD-komponentin käyttäminen lämpötilan mittaamiseen edellyttää tunnetun virran syöttämistä RTD-komponentin läpi ja jännitehäviön mittaamista, minkä jälkeen sovelletaan Ohmin lakia. (Kuvan lähde: Digi-Key)

Tämän peruskaavion piiritopologia on sama kuin mittausvastuksen käyttö virran määrittämiseksi kuorman kautta, mutta tässä tunnetut ja tuntemattomat muuttujat vaihtavat paikkaa. Virtamittauksessa vastus tunnetaan, mutta virtaa ei, joten laskutoimitus on I = V/R. RTD-komponentin tapauksessa virta tunnetaan, mutta vastusta ei, joten laskutoimitus on R = V/I.

PGA-vahvistusta tarvitaan signaalin eheyden ylläpitämiseen ja dynaamisen alueen maksimoimiseen, sillä RTD-mittauksen jännitetasot voivat vaihdella kymmenistä millivolteista satoihin millivoltteihin RTD-komponentin tyypistä ja lämpötilasta riippuen.

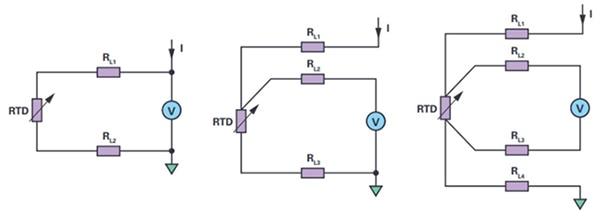

Virtalähteen, RTD-komponentin ja PGA-vahvistimen välinen fyysinen yhteys voidaan muodostaa kahdella, kolmella tai neljällä johtimella. Vaikka kaksi johdinta periaatteessa riittääkin, on otettava huomioon yhteysjohdinten IR-häviö sekä muita artefakteja. Käyttämällä kolmen tai neljän johtimen topologioita ja kehittyneempää Kelvin-kytkentää saadaan tarkempi ja tasalaatuisempi suorituskyky, vaikka tämä lisääkin johdotuskustannuksia (kuva 3).

Kuva 3: RTD-komponenttia voidaan käyttää ja mitata vain kahdella johtimella (vasemmalla), mutta kolmen johtimen (keskellä) ja jopa neljän (oikealla, Kelvin-kytkentä) käyttäminen mahdollistaa useiden johtimista johtuvien virhelähteiden poistamisen. (Kuvan lähde: Analog Devices)

Kuva 3: RTD-komponenttia voidaan käyttää ja mitata vain kahdella johtimella (vasemmalla), mutta kolmen johtimen (keskellä) ja jopa neljän (oikealla, Kelvin-kytkentä) käyttäminen mahdollistaa useiden johtimista johtuvien virhelähteiden poistamisen. (Kuvan lähde: Analog Devices)

Aloitamme terminologiasta ja standardeista

Kuten monilla erikoisaloilla, toiminnallisessa turvallisuudessa on monia alakohtaisia termejä, tietokokonaisuuksia ja akronyymeja, joita käytetään laajalti niihin liittyvissä keskusteluissa. Näihin kuuluvat seuraavat:

- FIT: vikaantumisten lukumäärä, jota voidaan odottaa miljardin (109) käyttötunnin aikana.

- FMEA: vikatilojen ja vaikutusten analysointiprosessi, jossa tarkistetaan mahdollisimman monta komponenttia, kokoonpanoa ja alijärjestelmää järjestelmän mahdollisten vikatilojen ja niiden syiden ja vaikutusten tunnistamiseksi.

- FMEDA: vikatilojen ja niiden vaikutusten analyysit sekä diagnostiset analyysit käyttäen järjestelmällistä analyysitekniikkaa osajärjestelmän/tuotetason vikaantumistaajuuden, vikatilojen ja diagnostiikkaominaisuuksien määrittämiseksi.

Järjestelmän kattava analysointi vaatii eri komponenttien FIT-tiedot ja FMEDA-analyysit. FMEA tarjoaa vain kvalitatiivista tietoa, kun taas FMEDA tarjoaa sekä kvalitatiivisia että kvantitatiivisia tietoja, joiden avulla käyttäjät voivat mitata vikatilojen kriittisyyden ja järjestää ne tärkeyden mukaan. FMEDA lisää riski-, vikatila-, vaikutus- ja diagnostiikka-analyysit sekä luotettavuustiedot.

- SIL-turvavaatimustaso: Jakautuu neljään erilliseen vaatimustasoon: SIL 1, SIL 2, SIL 3 ja SIL 4. Mitä korkeampi SIL-taso, sitä korkeampi on siihen liittyvä turvallisuustaso ja sitä pienempi todennäköisyys, että järjestelmä ei toimi oikein.

SIL 2 ‑luokitus tarkoittaa, että yli 90 % järjestelmän vioista voidaan diagnosoida. Järjestelmän suunnittelijan on todistettava sertifiointitaholle mahdolliset viat, olivatpa ne turvallisia vikoja tai vaarallisia vikoja, ja se, miten nämä viat voidaan diagnosoida.

- IEC 61508, jonka virallinen nimi on ”Sähköisten/elektronisten/ohjelmoitavien elektronisten turvallisuuteen liittyvien järjestelmien toiminnallinen turvallisuus” (ja jota kutsutaan epävirallisesti vain sähköisen toiminnallisen turvallisuuden standardiksi), spesifioi toiminnallisesti turvalliset ratkaisut. Se dokumentoi SIL-sertifioidun osan kehittämiseen tarvittavan suunnittelumenetelmän. Jokaista vaihetta varten on luotava dokumentaatio konseptista ja määritelmästä lähtien aina suunnitteluun, layoutiin, valmistukseen, kokoonpanoon ja testaamiseen asti.

Tämä prosessi tunnetaan nimellä Route 1S, ja se on monimutkainen. Route 1S -prosessille on kuitenkin vaihtoehto, jota kutsutaan Route 2S ‑menetelmäksi. Tämä menetelmä perustuu suureen määrään käytössä olevia laitteita erilaisissa lopputuotteissa ja järjestelmissä, jotka ovat olleet käytössä yhteensä tuhansien käyttötuntien ajan.

Route 2S ‑menetelmässä tuote voidaan silti sertifioida toimittamalla sertifiointiviranomaiselle todisteet seuraavista:

- kentällä käytössä olevien laitteiden määrä

- analyysi palautetuista tuotteista ja tiedot siitä, että palautukset eivät johtuneet itse komponentin virheistä

- käyttöturvallisuustiedote, jossa on yksityiskohtaiset tiedot vianmäärityksestä ja sen kattavuudesta

- nastojen ja sirun FMEDA.

RTD-liitäntöjen yhdistäminen SIL Route 2S ‑menetelmään

Järjestelmän sertifiointi on pitkä prosessi, koska kaikki järjestelmän osat on tarkistettava mahdollisten vikamekanismien varalta, ja vikojen diagnosointiin on useita menetelmiä. Jo sertifioitujen osien käyttö vähentää tarvittavaa työtä ja lyhentää sertifiointiprosessia.

Erittäin integroitu ja kypsä RTD-liitäntäkomponentti on avainasemassa Route 2S ‑sertifioinnin helpottamisessa, koska se on kokonainen ratkaisu ja voidaan siten täysin kuvata kentällä käyttöön ja vikoihin liittyvien tietojen avulla. Tämä poikkeaa useiden pienempien piirien käytöstä rakennuspalikkoina, sillä silloin niiden eri liitännät ja vuorovaikutus on analysoitava juuri käytettävää liitäntäkokoonpanoa varten.

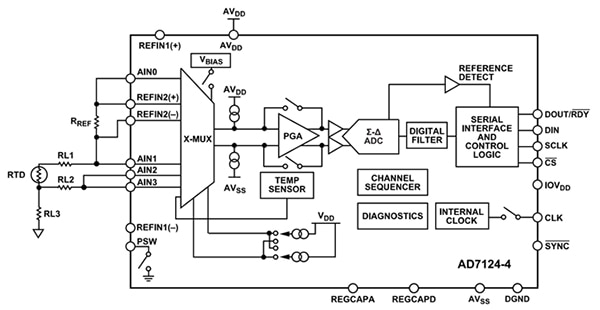

Esimerkkejä tästä ovat nelikanavainen AD7124-4 (kuva 4) ja vastaava kahdeksankanavainen AD7124-8 (joita tästä lähtien kutsutaan yhteisesti nimellä AD7124 kuvattaessa niiden yhteisiä ominaisuuksia). Nämä komponentit sopivat hyvin Route 2S ‑menetelmään niiden sulautettujen itsetestaus- ja diagnostiikkaominaisuuksien sekä niille kertyneiden käyttökokemusten ansiosta.

Kuva 4: Nelikanavainen AD7124-4 on toiminnallisesti täydellinen RTD-anturin ja suorittimen välinen signaaliketju. (Kuvan lähde: Analog Devices)

Kuva 4: Nelikanavainen AD7124-4 on toiminnallisesti täydellinen RTD-anturin ja suorittimen välinen signaaliketju. (Kuvan lähde: Analog Devices)

Nämä integroidut piirit ovat täydellisiä ratkaisuja monikanavaiseen RTD-mittaukseen, ja ne sisältävät kaikki tarvittavat rakennuspalikat anturista digitoituun lähtöön ja tiedonsiirtoon siihen kytketyn mikrokontrollerin kanssa. Ne sisältävät monikanavaisen multiplekserin, PGA-vahvistimen, 24-bittisen sigma-delta AD-muuntimen, RTD-komponenttien virtalähteet, referenssijännitteet sisäistä toimintaa varten, järjestelmäkellon, analogisen ja digitaalisen suodatuksen sekä kolme- tai neljäjohtimiset sarjaliitännät SPI-, QSPI-, MICROWIRE- ja DSP-yhteensopiville kytkennöille.

Nämä toiminnot eivät kuitenkaan sinällään muodosta perustetta Route 2S ‑SIL-hyväksynnälle. Toiminnallisesti turvalliseen ratkaisuun tarvitaan useita sulautettuja diagnostiikkatoimintoja kaikkia RTD-järjestelmän muodostavia toimintoja varten. AD7124-piirin useat sisäänrakennetut diagnostiikkatoiminnot minimoivat sekä ratkaisun kompleksisuuden että suunnitteluajan ja poistavat tarpeen kopioida signaaliketju diagnostiikkaa varten.

Näitä diagnostiikkaominaisuuksia ovat muun muassa virransyötön, referenssijännitteen ja analogisen tulon valvonta, RTD-komponentille tulevan avoimen johtimen havaitseminen, muunnosten ja kalibroinnin suorituskyvyn seuranta, signaaliketjun toiminnan seuranta, luku- ja kirjoitustoimintojen valvonta ja rekisterien sisällön seuranta.

Miten näistä ylätason toiminnoista päästään tarvittavaan sirulle toteutettuun diagnostiikkaan? Vastaus on monisyinen ja sisältää muun muassa seuraavat:

SPI-diagnostiikka: suoritin luo jokaista AD7124-piirille tehtävää kirjoitusta varten CRC-arvon, joka liitetään ADC-piirille lähetettäviin tietoihin. Tämän jälkeen ADC luo vastaanotettujen tietojen perusteella oman CRC-arvonsa ja vertaa sitä suorittimen lähettämään CRC-arvoon. Jos arvot täsmäävät, tiedot ovat ehjiä ja ne kirjoitetaan vastaavaan sirulla olevaan rekisteriin.

Jos arvot eivät täsmää, tiedonsiirrossa on tapahtunut virhe ja integroitu piiri aktivoi virheindikaation, joka ilmaisee tietojen vioittuneen. AD7124 suojaa myös itseään siten, ettei korruptoituneita tietoja kirjoiteta rekisteriin.

Vastaavaa CRC-menetelmää käytetään, kun tietoja luetaan AD7124-piiristä järjestelmän suorittimeen. Lopuksi liitäntä laskee myös kellopulsseja varmistaakseen, että jokaisessa luku- tai kirjoituskehyksessä on vain kahdeksan tällaista pulssia, mikä varmistaa, että kellohäiriötä ei ole tapahtunut.

Muistitarkistukset: CRC-arvoa käytetään myös rekisterin sisällön vahvistamiseen käynnistyksen yhteydessä tai aina, kun sirun rekisterejä muutetaan (esimerkiksi vahvistusta muutettaessa). CRC-prosessi suoritetaan myös säännöllisesti sen varmistamiseksi, että mikään muistin biteistä ei ole ”kääntynyt” kohinan tai muiden syiden seurauksena. Jos datassa havaitaan muutos ja suorittimelle sitten ilmoitetaan rekisteriasetusten vioittuneen, se voi nollata ADC-piirin ja ladata rekisterit uudelleen.

Signaaliketjun tarkistukset: kaikki kriittiset staattiset jännitteet voidaan tarkistaa ADC-piirin kautta, mukaan lukien jännitetasot, LDO-jännitteensäätimen lähdöt ja referenssijännitteet. LDO-piirin ylitse olevan ulkoisen kondensaattorin läsnäolo tai puuttuminen voidaan myös tarkistaa. Lisäksi ADC-tuloon voidaan syöttää tunnettu jännite ADC-piirin ja vahvistustoiminnon asetusten tarkistamista varten. Lisäksi analogisiin tuloihin voidaan syöttää tunnettu virta avoimen tai oikosulussa olevan RTD-komponentin tarkistamiseksi.

Muunnokset ja kalibrointi: ADC-muunnoksen tuloksia seurataan jatkuvasti, koska ne menevät nollaan tai maksimiarvoon, tämä viittaa ongelmaan. ADC-piirin ytimessä olevan modulaattorin bittivirtaa valvotaan sen varmistamiseksi, että se ei ole saturoitunut, ja jos saturaatio tapahtuu (eli modulaattorista on tullut 20 peräkkäistä ykköstä tai nollaa), järjestelmä asettaa virheilmoituksen.

Pääkellotaajuus: tämä kellotaajuus ei ainoastaan ohjaa muuntonopeuksia, vaan myös määrittää 50/60 hertsin (Hz) digitaalisten suodattimien rajataajuudet. AD7124-piirin sisäisen rekisterin avulla kumppaniprosessori voi ajoittaa ja siten tarkistaa pääkellon tarkkuuden.

Lisäominaisuudet: AD7124 sisältää lämpötila-anturin, jota voidaan käyttää myös sirun lämpötilan tarkkailuun. Molemmissa versioissa on 4 kilovoltin (kV) ESD-luokitus, joka takaa robustin suorituskyvyn, ja molemmat käyttävät 5 × 5 millimetrin LFCSP-koteloa, joka sopii luonnostaan turvallisiin ratkaisuihin.

AD7124-4- ja AD7124-8-piirien sisäisen kompleksisuuden, sofistikoituneisuuden ja kehittyneiden itsetestausominaisuuksien vuoksi on järkevää tarjota tapoja näiden integroitujen piirien kokeilemiseen ja arviointiin.

Analog Devices tarjoaa tähän tarkoitukseen kaksi toisiinsa liittyvää korttia: EVAL-AD7124-4SDZ-evaluointikortti iirille AD7124-4 (kuva 5) ja sen kumppani EVAL-SDP-CB1Z SDP (järjestelmän esittelyalusta)/liitäntäkortti (kuva 6). Edellinen on tarkoitettu nimenomaisesti piiriä AD7124-4 varten ja toimii yhdessä jälkimmäisen kanssa, joka tarjoaa yhteyden käyttäjän tietokoneeseen ja arviointiohjelmistoon USB-linkin kautta.

Kuva 5: EVAL-AD7124-4SDZ on evaluointikortti AD7124-4-piiriä varten. (Kuvan lähde: Analog Devices)

Kuva 5: EVAL-AD7124-4SDZ on evaluointikortti AD7124-4-piiriä varten. (Kuvan lähde: Analog Devices)

Kuva 6: EVAL-SDP-CB1Z/liitäntäkortti täydentää EVAL-AD7124-4SDZ-evaluointikorttia ja tarjoaa USB-yhteyden isäntätietokoneeseen. (Kuvan lähde: Analog Devices)

Kuva 6: EVAL-SDP-CB1Z/liitäntäkortti täydentää EVAL-AD7124-4SDZ-evaluointikorttia ja tarjoaa USB-yhteyden isäntätietokoneeseen. (Kuvan lähde: Analog Devices)

Evaluointijärjestelyä voidaan tukea AD7124-4 EVAL+-ohjelmistolla, jolla voidaan täysin määrittää AD7124-4-laiterekisteritoiminnot ja testata integroidun piirin toimintaa. Se tarjoaa myös aika-alueanalyysin aaltomuotokaavioina, histogrammeina ja niihin liittyvinä kohina-analyyseina ADC-piirin suorituskyvyn arvioimiseksi.

Siirtyminen toiminnallisesti turvalliseen suunnitteluun

On tärkeää huomata, että AD7124-4 ja AD7124-8 eivät ole SIL-luokiteltuja, joten niitä ei ole suunniteltu ja kehitetty käyttäen IEC 61508 ‑standardissa määriteltyjä kehitysohjeita. Mikäli lopullinen käyttökohde kuitenkin ymmärretään ja erilaisia diagnostiikkaominaisuuksia käytetään asianmukaisesti, ne voidaan arvioida SIL-luokitellussa laitteessa käyttöä varten.

Route 1S ‑sertifiointimenetelmässä on useita huomioon otettavia tekijöitä systeemisten ja satunnaisten vikojen analysoimiseksi ja korjaamiseksi. Systeemiset viat johtuvat suunnittelu- tai valmistusvirheistä, kuten kohinaherkkä keskeytys, joka johtuu siitä, että ulkoisesta keskeytysnastasta puuttuu suodatus, tai riittämättömästä signaalin liikkumavarasta. Sen sijaan satunnaiset viat johtuvat fyysisistä syistä, kuten korroosiosta, lämpörasituksesta tai kulumisesta.

Erästä tärkeää tekijää kutsutaan vaaralliseksi havaitsemattomaksi vikaantumiseksi, johon puututaan useilla tekniikoilla. Satunnaisten vikojen minimoimiseksi suunnittelijat käyttävät yhtä tai kaikkia seuraavasta kolmesta taktiikasta:

- luotettavammat komponentit, joita kuormitetaan vähemmän

- diagnostiikkaa, joka perustuu laitteiston tai ohjelmiston kautta toteutettuihin sisäänrakennettuihin tunnistusmekanismeihin

- vikasieto redundanteilla virtapiireillä. Lisäämällä redundantti polku järjestelmä voi kestää yksittäisen vikaantumisen. Tätä kutsutaan HFT 1 ‑järjestelmäksi, mikä tarkoittaa, että yksi vikaantuminen ei voi aiheuttaa järjestelmän virhetoimintaa.

Yksi työkalu SIL-tason kattavuuden ymmärtämiseen on matriisi, joka näyttää vaarattomien vikojen osuuden (SFF) (diagnostiikkakattavuuden määrän) ja laitteistovikatoleranssin (redundanssi) (kuva 7).

|

|||||||||||||||||||||||

Kuva 7: Tämä matriisi kuvastaa vaarattomien vikojen osuutta (SFF) verrattuna laitteistovikatoleranssiin (HFT) ja antaa käsityksen SIL-kattavuudesta. (Kuvan lähde: Analog Devices)

Riveillä esitetään diagnostiikan kattavuus, kun taas sarakkeissa esitetään laitteistovikatoleranssi. HFT 0 tarkoittaa, että jos järjestelmässä on yksi vika, turvatoiminto menetetään. Korkeampi diagnostiikan määrä vähentää tarvittavaa järjestelmän redundanssimäärää tai parantaa ratkaisun SIL-tasoa samalla redundanssitasolla (siirtymällä matriisissa alaspäin).

Huomaa, että näitä laitteita käyttävän tyypillisen lämpötilasovelluksen FMEDA näyttää vaarattomien vikojen osuuden (SFF) olevan yli 90 % IEC 61508 -standardin mukaan. Normaalisti tämän tason kattavuuden tarjoamiseksi redundanssin avulla tarvittaisiin kaksi perinteistä ADC-piiriä, mutta AD4172 vaatii vain yhden ADC-piirin, mikä tarjoaa merkittäviä säästöjä materiaalikuluissa (BOM) ja piirilevyltä vaaditussa tilassa.

SIL-luokiteltujen mallien dokumentointi

Route 1S ‑sertifioinnin saamiseksi tarvitaan kattavaa dokumentaatiota. Tarvittavia lähdeasiakirjoja ovat muun muassa seuraavat:

- turvallisuustiedot (SIL-luokiteltua osaa varten tarkoitettu turvallisuusopas)

- nastojen FMEDA ja sirun FMEDA, vikatilat, vaikutukset ja analyysit molemmista

- liitteen F ‑tarkistuslista (määritelty standardissa IEC 61508)

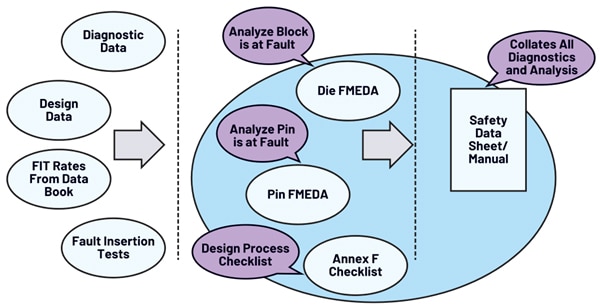

Tämä dokumentaatio tulee puolestaan useista eri lähteistä (kuva 8):

- Teknisten tietojen diagnostiikkatiedot sisältävät kaikki osassa käytettävissä olevat diagnostiikkaominaisuudet.

- Suunnittelutiedot viittaavat sisäisiin tietoihin. Esimerkiksi osan kunkin sisäisen lohkon pinta-ala sirussa ja vaikutus.

- FIT ja eri komponenttien FIT-arvot ovat saatavilla tietokirjasta.

- Vianlisäystestit tehdään lohkoille, joita ei voi analysoida suunnittelu- ja diagnostiikkatietojen avulla. Nämä testit suunnitellaan sovellusvaatimusten perusteella, ja vianlisäystestien tuloksia käytetään FMEDA- ja FMEA-asiakirjojen vahvistamiseen.

Kuva 8: Monipuoliset dokumentointilähteet kootaan ja niistä muodostetaan SIL-sertifiointiin tarvittava tietopaketti. (Kuvan lähde: Analog Devices)

Kuva 8: Monipuoliset dokumentointilähteet kootaan ja niistä muodostetaan SIL-sertifiointiin tarvittava tietopaketti. (Kuvan lähde: Analog Devices)

Tarkempia yksityiskohtia:

- Turvallisuusoppaassa eli turvallisuustiedoissa käytetään kaikkia koottuja tietoja, jotka tarvitaan piirien AD7124-4 tai AD7124-8 integrointia varten. Siihen kootaan kaikki diagnostiikka ja analyysit, joita saadaan eri asiakirjoista ja tietojoukoista.

- Piirien AD7124-4 ja AD7124-8 sirun FMEDA analysoi käyttökohteen piirikaavion päälohkot, tunnistaa vikatilat ja vaikutukset sekä tarkistaa tietyn turvallisuustoiminnon diagnoosin ja analyysit. Esimerkiksi kellomoduulin analyysi näyttää vikatilat, kunkin niistä vaikutuksen lähtöön, diagnostisen kattavuuden määrän ja vaikutusanalyysin (kuva 9).

|

Kuva 9: Tässä taulukossa määritetään pääkellolohkon vikatila, vaikutukset, diagnostiikka ja analyysi. (Kuvan lähde: Analog Devices)

Näistä sirun FMEDA-tiedoista saadaan turvallisten vikojen, vaarallisten havaittujen vikojen ja vaarallisten havaitsemattomien vikojen vikaantumistaajuuksien kvantitatiivinen esitys. Kaikkia näitä käytetään SFF-arvon laskemiseen.

Nastan FDEMA tarkastelee vikoja eri näkökulmasta. Se analysoi erilaisia vikoja piirien AD7124-4 ja AD7124-8 nastoissa ja niiden vaikutuksia RTD-sovellukseen. Se tekee tämän jokaiselle yksittäiselle nastalle ja kuvaa tapauksen lopputuloksen, kun nasta avautuu, menee oikosulkuun virtalähteen/maan kanssa tai oikosulkuun viereisten nastojen kanssa.

Liitteessä F oleva tarkistuslista on suunnittelutoimenpiteiden tarkistuslista systeemisten vikojen välttämiseksi. Se käsittää seuraavat:

- tuotteen yleiskatsaus

- sovellustiedot

- turvallisuuskonsepti

- elinkaaren ennustukset

- FIT

- FMEDA-laskelmat – SFF ja DC

- laitteiston turvamekanismit

- diagnostiikan kuvaus

- EMC-robustisuus

- käyttö redundanttikonfiguraatioissa

- liitteet ja asiakirjaluettelo.

Yhteenvetona voidaan todeta, että uuden komponentin toiminnallisen turvallisuuden sertifiointi Route 1S -menetelmän kautta on pitkä, monimutkainen, aikaa vievä, intensiivinen ja vaativa prosessi. Onneksi Route 2S, kuten edellä mainittiin, on joillekin komponenteille käytettävissä oleva vaihtoehtoinen lähestymistapa.

Route 2S: Vaihtoehtoinen menetelmä

Route 2S ‑menetelmää voidaan käyttää julkaistulle osalle, josta on käyttökokemusta ja -tietoja kentältä ja joka on ”hyväksi havaittu”. Se perustuu analyysiin asiakaspalautuksista ja toimitettujen laitteiden määrästä. Sitä ei voi käyttää sellaisten uusien osien kanssa, joista on vain vähän tai ei lainkaan tietoa toiminnasta todellisessa käytössä.

Route 2S sallii SIL-sertifioinnin ikään kuin osa olisi täysin analysoitu IEC 61508 ‑standardin mukaisesti. Se on moduulien ja järjestelmien suunnittelijoiden käytettävissä, jos he ovat aiemmin käyttäneet kyseessä olevaa integroitua piiriä ja tietävät vikaantumistaajuuden kentältä. Sulautetut testi- ja vahvistusominaisuudet sekä suorituskykytiedot tekevät AD7214-4- ja AD7214-8-piireistä hyviä Route 2S ‑ehdokkaita.

Route 2S -menetelmän käyttäminen edellyttää yksityiskohtaisia ja tilastollisesti merkitseviä tietoja palautuksista ja vikaantumisista kentällä. Tämän vaatimuksen täyttäminen on paljon vaikeampaa integroitujen piirien toimittajille kuin piirilevyjen tai moduulien toimittajille. Syynä on se, että ensin mainitulla ei yleensä ole riittävästi tietoa lopullisesta käyttökohteesta tai siitä, kuinka suuri prosenttiosuus kentällä vikaantuneista yksiköistä palautetaan heille analysoitavaksi.

Yhteenveto

Route 1S ‑menetelmä uusien tuotteiden toiminnallisen turvallisuuden sertifioimiseksi on perusteellinen, kattava ja yksityiskohtainen. Se on myös teknisesti haastava ja ehdottomasti aikaa vievä. Sen sijaan Route 2S ‑prosessin avulla julkaistuja tuotteita voidaan sertifioida kenttäkokemuksen sekä vikaantumis- ja analyysitietojen perusteella. Tämä on hyödyllinen vaihtoehto, jota RTD-kytkentäpiirit AD7214-4 ja AD7214-8 tukevat, koska niillä on tarvittava historia. Yhtä tärkeää on se, että nämä integroidut piirit sisältävät monia sulautettuja diagnostiikka- ja itsetestaustoimintoja ja -ominaisuuksia, joiden ansiosta ne ovat sopivia ehdokkaita tällaiseen sertifiointiin.

Vastaavaa aineistoa

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.