Rinnakkaisprosessoriarkkitehtuuri: sulautettu järjestelmäarkkitehtuuri nopeaa prototyyppikehitystä varten

2021-07-06

Toimituksen huomautus – Vaikka rinnakkaisprosessoriarkkitehtuuri tunnetaan digitaalisesta prosessointikyvystä ja suoritustehosta, se tarjoaa sulautettujen järjestelmien suunnittelijoille myös mahdollisuuksia toteuttaa projektinhallintastrategioita, jotka sekä laskevat kehityskustannuksia että lyhentävät markkinoilletuontiaikaa. Tässä artikkelissa keskitytään erityisesti erillisen mikrokontrollerin (MCU) ja erillisen ohjelmoitavan porttimatriisin (FPGA) yhdistelmään ja esitellään, miten tämä arkkitehtuuri soveltuu tehokkaaseen ja iteratiiviseen suunnitteluprosessiin. Arkkitehtuurin etuja tarkastellaan tutkittujen lähteiden, empiiristen havaintojen ja tapaustutkimusten avulla, ja artikkelissa esitellään myös esimerkkisovelluksia. Tämän artikkelin päätteeksi sulautettujen järjestelmien suunnittelijalla on parempi käsitys siitä, milloin ja miten tämä monipuolinen laitteistoarkkitehtuuri kannattaa ottaa käyttöön.

Johdanto

Sulautettujen järjestelmien suunnittelija on suunnittelurajoitusten, suorituskykyodotusten sekä aikataulu- ja budjettihuolten välissä. Itse asiassa nykyaikaisen projektinhallinnan muotisanojen ja fraasien ristiriitaisuus korostaa entisestään tämän roolin epävarmaa luonnetta: ”epäonnistu nopeasti”, ”ole ketterä”, ”varmista tulevaisuuden vaatimusten täyttäminen” ja ”ole mullistava”. Akrobatia, jolla näitä odotuksia edes yritetään täyttää, voi olla tuskastuttavaa, ja silti näitä odotuksia esitetään ja vahvistetaan edelleen kaikilla markkina-alueilla. Tarvitaan suunnittelutapa, joka mahdollistaa evolutiivisen iteratiivisen prosessin noudattamisen, ja aivan kuten useimmissa sulautetuissa järjestelmissä, se alkaa laitteistoarkkitehtuurista.

Rinnakkaisprosessoriarkkitehtuuri on laitteistoarkkitehtuuri, joka on tunnettu siitä, että siinä yhdistyvät sekä mikrokontrollerin (MCU) että ohjelmoitavan porttimatriisitekniikan (FPGA) vahvuudet. Se voi tarjota sulautetun järjestelmän suunnittelijalle prosessin, joka täyttää kaikkein korkeimmatkin vaatimukset ja silti tarjoaa joustavuutta, joka tarvitaan sekä tunnettuihin että tuntemattomiin haasteisiin vastaamiseksi. Tarjoamalla laitteiston, joka pystyy mukautumaan iteratiivisesti, suunnittelija voi demonstroida edistysaskelia projektissa, saavuttaa kriittiset välitavoitteet ja hyödyntää täysin nopeaa prototyyppikehitysprosessia.

Tässä prosessissa on keskeisiä projektin välitavoitteita, joista kukin tarjoaa oman ainutlaatuisen lisäarvonsa kehitystyöhön. Tässä artikkelissa näihin välitavoitteisiin viitataan seuraavilla termeillä: digitaalinen signaalinkäsittely mikrokontrollerilla, järjestelmänhallinta mikrokontrollerilla ja tuotteen käyttöönotto.

Tämän artikkelin lopussa osoitetaan, että joustava laitteistoarkkitehtuuri voi soveltua jäykempää lähestymistapaa paremmin nykyaikaisten sulautettujen järjestelmien suunnitteluun. Lisäksi tämä lähestymistapa voi sekä laskea projektin kustannuksia että lyhentää markkinoilletuontiaikaa. Tätä näkökantaa puolustetaan argumenttien, esimerkkien ja tapaustutkimusten avulla. Tarkasteltaessa kunkin välitavoitteen arvoa tämän arkkitehtuurin mahdollistaman joustavan suunnittelun puitteissa, käy selväksi, että adaptiivinen laitteistoarkkitehtuuri edistää tehokkaasti sulautettujen järjestelmien suunnittelua.

Rinnakkaisprosessoriarkkitehtuurin vahvuuksien tutkiminen: suunnittelun joustavuus ja huipputehokas prosessointi

Ohjelmoitavien porttimatriisiratkaisujen yleinen käyttökohde on suora liitäntä nopeaan analogia-digitaalimuuntimeen (ADC). Signaali digitoidaan, luetaan porttimatriisiin ja sitten signaaliin käytetään joitakin digitaalisen signaalinkäsittelyn (DSP) algoritmeja. Lopuksi ohjelmoitava porttimatriisi tekee sitten päätökset tulosten perusteella.

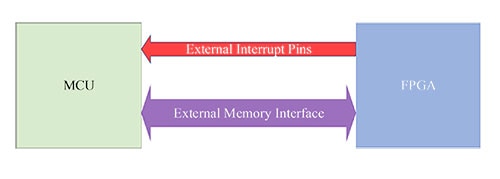

Tällainen sovellus toimii esimerkkinä kautta tämän artikkelin. Kuvassa 1 esitetään lisäksi yleinen rinnakkaisprosessoriarkkitehtuuri, jossa mikrokontrolleri ja ohjelmoitava porttimatriisi on yhdistetty mikrokontrollerin ulkoisen muistirajapinnan kautta. Ohjelmoitavaa porttimatriisia kohdellaan ikään kuin se olisi SRAM (Static Random Access Memory) -muisti. Signaalit palaavat porttimatriisista mikrokontrolleriin ja toimivat laitteiston keskeytyslinjoina ja tilanilmaisimina. Näin porttimatriisi voi ilmoittaa mikrokontrollerille kriittiset tilat. Esimerkiksi sen, että ADC-muunnos on valmis, että prosessoinnissa on tapahtunut virhe tai että on tapahtunut jotain muuta merkittävää.

Kuva 1: Yleinen rinnakkaisprosessorikaavio (MCU + FPGA). (Kuvan lähde: CEPD)

Kuva 1: Yleinen rinnakkaisprosessorikaavio (MCU + FPGA). (Kuvan lähde: CEPD)

Rinnakkaisprosessoriarkkitehtuuria käyttävän lähestymistavan vahvuudet näkyvät luultavasti parhaiten kunkin edellä mainitun välitavoitteen tuloksissa. Arvoa ei arvioida pelkästään luetteloimalla tehtävän tai vaiheen saavutukset, vaan myös arvioimalla mitä nämä saavutukset mahdollistavat. Vastaukset seuraaviin kysymyksiin auttavat arvioimaan välitavoitteen tulosten kokonaisarvoa:

- Voivatko muut tiimin jäsenet jatkaa nyt nopeammin, kun projektin riippuvuudet ja pullonkaulat on poistettu?

- Miten välitavoitteen saavutukset mahdollistavat uudet rinnakkaiset toteutuspolut?

Välitavoite – digitaalinen signaalinkäsittely mikrokontrollerilla

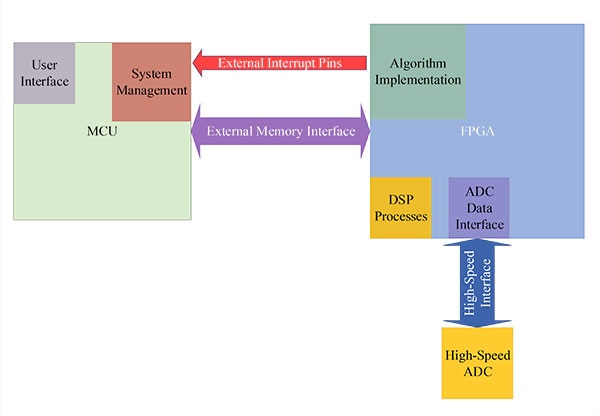

Kuva 2: Arkkitehtuuri – digitaalinen signaalinkäsittely mikrokontrollerilla. (Kuvan lähde: CEPD)

Kuva 2: Arkkitehtuuri – digitaalinen signaalinkäsittely mikrokontrollerilla. (Kuvan lähde: CEPD)

Ensimmäinen kehitysvaihe, jonka tämä laitteistoarkkitehtuuri mahdollistaa, asettaa mikrokontrollerin keskipisteeseen. Mikrokontrollerin ja suoritettavan ohjelmiston kehittäminen vie kaiken kaikkiaan vähemmän resursseja ja aikaa kuin ohjelmoitavan porttimatriisin ja laitteistokuvauskielen (HDL) käyttö. Kun tuotekehitys aloitetaan käyttämällä mikrokontrolleria ensisijaisena prosessorina, algoritmit voidaan toteuttaa, testata ja validoida nopeammin. Näin algoritmiset ja loogiset virheet voidaan havaita suunnitteluprosessin alkuvaiheessa, minkä ansiosta myös huomattavia osia signaaliketjusta voidaan testata ja validoida.

Ohjelmoitavan porttimatriisin rooli tässä ensimmäisessä välitavoitteessa on toimia nopeana tiedonkeruurajapintana. Sen tehtävänä on vastaanottaa luotettavasti dataa nopeasta analogia-digitaalimuuntimesta, ilmoittaa mikrokontrollerille, että dataa on saatavilla, ja esittää tämä data mikrokontrollerin ulkoisessa muistirajapinnassa. Vaikka tähän rooliin ei sisälly HDL-pohjaisten DSP-prosessien tai muiden algoritmien suorittamista, se on silti erittäin tärkeä.

Tässä vaiheessa suoritettu ohjelmoitavan porttimatriisin kehitys luo perustan tuotteen lopulliselle menestykselle sekä tuotekehitystyön aikana että sen markkinoilletuonnin jälkeen. Keskittymällä vain matalan tason rajapintaan näiden keskeisten toimintojen testaamiseen voidaan käyttää riittävästi aikaa. Vasta kun porttimatriisi hoitaa tämän rajapintaroolin varmasti ja luotettavasti, tämä välitavoite voidaan viimeistellä luottavaisin mielin.

Tämän ensimmäisen välitavoitteen tärkeimpiin tuloksiin kuuluvat seuraavat edut:

- Koko signaalipolku – kaikki vahvistukset, vaimennukset ja muunnokset – testataan ja validoidaan.

- Projektin kehitysaika ja -vaiva vähentyy toteuttamalla algoritmit aluksi ohjelmistolla (C/C++). Tästä on huomattavaa hyötyä projektin johdolle ja muille sidosryhmille, joiden täytyy nähdä projektin toteuttamiskelpoisuus ennen tulevien suunnitteluvaiheiden hyväksymistä.

- Algoritmien toteuttamisesta C/C++-ohjelmistossa saatavat kokemukset ovat siirrettävissä suoraan HDL-toteutuksiin käyttämällä työkaluja, jotka muuntavat ohjelmiston HDL:ksi, esimerkkinä Xilinx HLS.

Välitavoite – järjestelmänhallinta mikrokontrollerilla

Kuva 3: Arkkitehtuuri – järjestelmänhallinta mikrokontrollerilla. (Kuvan lähde: CEPD)

Kuva 3: Arkkitehtuuri – järjestelmänhallinta mikrokontrollerilla. (Kuvan lähde: CEPD)

Toisessa tämän rinnakkaisprosessorikäytännön tarjoamassa kehitysvaiheessa DSP-prosessit ja algoritmitoteutukset siirretään mikrokontrollerista ohjelmoitavaan porttimatriisiin. Porttimatriisi vastaa edelleen erittäin nopeasta ADC-rajapinnasta, mutta sen tarjoama nopeus ja rinnakkaisuus otetaan täysimääräisesti käyttöön vasta sen omaksuessa nämä muut roolit. Lisäksi siinä voidaan käyttää ja suorittaa samanaikaisesti useita DSP-prosesseja ja algoritmikanavia toisin kuin mikrokontrollerissa.

Suunnittelija siirtää mikrokontrollerin toteutuksesta saadun kokemuksen ja luottavaisuuden tähän seuraavaan välitavoitteeseen. Sellaiset työkalut kuten aiemmin mainittu Xilinx Vivado HLS tarjoavat toiminnallisen käännöksen suoritettavasta C/C++-koodista syntetisoitavaksi HDL:ksi. Ajoitusrajoitukset, prosessiparametrit ja muut halutut ominaisuudet on edelleen määriteltävä ja toteutettava, mutta ydintoiminnot säilytetään ja käännetään porttimatriisirakenteeseen.

Tässä välitavoitteessa mikrokontrollerilla on järjestelmäpäällikön rooli. Mikrokontrolleri valvoo, päivittää ja raportoi porttimatriisin tila- ja ohjausrekistereitä. Lisäksi mikrokontrolleri ohjaa käyttöliittymää (UI). Tämä käyttöliittymä voi olla verkkopalvelin, jota käytetään Ethernet- tai Wi-Fi-yhteyden kautta. Se voi myös olla teollinen kosketusnäyttöliittymä, jota käyttäjät voivat käyttää käyttöpisteessä. Mikrokontrollerin uuden tarkemman roolin tärkein anti on tämä: laskentaintensiivisistä prosessointitehtävistä vapauttamisen ansiosta sekä mikrokontrolleria että ohjelmoitavaa porttimatriisia hyödynnetään nyt niissä tehtävissä, joihin ne soveltuvat hyvin.

Tämän välitavoitteen tärkeimpiin tuloksiin kuuluvat seuraavat edut:

- Ohjelmoitava porttimatriisi mahdollistaa DSP-prosessien rinnakkaisen suorituksen ja algoritmien nopean toteutuksen.Mikrokontrolleri tarjoaa responsiivisen ja virtaviivaistetun käyttöliittymän ja hallinnoi tuotteen prosesseja.

- Koska ne on kehitetty ja validoitu ensin mikrokontrollerissa, algoritmeihin liittyvät riskit vähenevät ja nämä edut hyödynnetään syntetisoitavassa HDL-kielessä. Työkalut, kuten Vivado HLS, helpottavat tätä kääntämistä. Lisäksi porttimatriiseihin liittyviä riskejä voidaan vähentää integroiduilla simulointityökaluilla, kuten Vivado-suunnittelupaketilla.

- Sidosryhmät eivät altistu merkittäville riskeille, kun prosessit siirretään ohjelmoitavaan porttimatriisiin. Sen sijaan he pääsevät näkemään ja nauttimaan porttimatriisin nopeuden ja rinnakkaisuuden tarjoamista eduista. Suorituskyky paranee merkittävästi, ja nyt voidaan keskittyä tämän ratkaisun tuotantokuntoon saattamiseen.

Välitavoite – tuotteen käyttöönotto

Kun laskentaintensiivinen prosessointi hoidetaan ohjelmoitavassa porttimatriisissa ja mikrokontrolleri vastaa järjestelmänhallinta- ja käyttöliittymätehtävistä, tuote on valmis käyttöönotettavaksi. Tässä artikkelissa ei puolleta alfa- ja beta-versioiden ohittamista, vaan tässä välitavoitteessa painotetaan ominaisuuksia, jotka rinnakkaisprosessoriarkkitehtuuri tarjoaa tuotteen käyttöönottoa varten.

Sekä mikrokontrolleri että ohjelmoitava porttimatriisi ovat laitteita, jotka voidaan päivittää jälkikäteen. Useiden edistysaskelien ansiosta ohjelmoitavan porttimatriisin päivitys ovat yhtä helppoa kuin ohjelmistopäivitys. Koska ohjelmoitava porttimatriisi on mikrokontrollerin osoitettavissa olevalla muistialueella, mikrokontrolleri voi toimia koko järjestelmän yhteyspisteenä: se voi vastaanottaa päivityksiä sekä itselleen että porttimatriisille. Päivitykset voidaan ajoittaa, jakaa ja mukauttaa loppukäyttäjäkohtaisesti haluttujen ehtojen mukaan. Kaiken lisäksi käyttäjä- ja käyttötapauslokit voidaan tallentaa ja liittää vastaaviin versiotietoihin. Näiden datajoukkojen avulla suorituskykyä voidaan edelleen hioa ja parantaa myös sen jälkeen, kun tuote on otettu käyttöön.

Koko järjestelmän päivitettävyyden vahvuudet tulevat ehkä parhaiten esiin avaruudessa käytettävissä sovelluksissa. Kun tuote on lähetetty avaruuteen, ylläpito ja päivitykset on tehtävä etänä. Tämä voi olla yhtä yksinkertaista kuin loogisten ehtojen muuttaminen tai yhtä monimutkaista kuin tietoliikennemodulointimenetelmän päivittäminen. Porttimatriisitekniikoiden ja rinnakkaisprosessoriarkkitehtuurin tarjoama ohjelmoitavuus mahdollistaa koko tämän ominaisuuksien kirjon ja samalla säteilynkestävien komponenttien valinnan.

Tämän välitavoitteen viimeinen keskeinen seikka on kustannusten asteittainen vähennys. Tässä välitavoitteessa voidaan toteuttaa myös kustannussäästötoimenpiteet, osaluettelon muutokset ja muut optimoinnit. Tuotteen ollessa yleisessä käytössä voi selvitä, että se voi toimia yhtä hyvin halvemmalla mikrokontrollerilla tai pienitehoisemmalla ohjelmoitavalla porttimatriisilla. Rinnakkaisprosessorin ansiosta arkkitehtuurisuunnittelijoiden ei tarvitse käyttää komponentteja, joiden ominaisuudet ylittävät sovelluksen tarpeet. Jos lisäksi jotain komponenttia ei ole enää saatavilla, arkkitehtuuri mahdollistaa uusien komponenttien integroinnin ratkaisuun. Näin ei ole yhden sirun, System on a chip (SoC) -arkkitehtuurin tai korkeatehoisen DSP:n tai mikrokontrollerin kanssa, joka yrittää hoitaa tuotteen kaiken prosessoinnin. Rinnakkaisprosessoriarkkitehtuuri on hyvä yhdistelmä tehokkuutta ja joustavuutta antaen suunnittelijalle enemmän valinnanvaraa ja vapauksia sekä kehitysvaiheissa että tuotaessa tuote markkinoille.

Aiheeseen liittyvä tutkimus ja tapaustutkimukset

Esimerkki satelliittiviestinnästä

Lyhyesti sanottuna rinnakkaisprosessorin tärkeys on vähentää ensisijaisen prosessoriyksikön kuormitusta siten, että tehtävät suoritetaan laitteistoissa, joissa voidaan hyödyntää laitteistokiihdytystä ja virtaviivaistettua suoritusta. Tällaisessa ratkaisussa etuna on laskentanopeuden ja -kapasiteetin nettokasvu ja, kuten tässä artikkelissa esitetään, kehityskustannusten vähennys ja kehitysajan lyheneminen. Kenties yksi näistä eduista vakuuttavimmin hyötyvistä alueista ovat avaruusviestintäjärjestelmät.

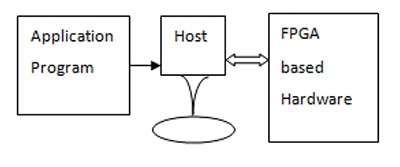

G. Prasad ja N. Vasantha kuvaavat julkaisussaan FPGA based hardware as coprocessor (FPGA-pohjainen laitteisto rinnakkaisprosessorina) yksityiskohtaisesti, miten ohjelmoitavan porttimatriisin suorittama tietojenkäsittely täyttää satelliittiviestintäjärjestelmien laskentatarpeet ilman sovelluskohtaisten integroitujen piirien (ASIC) korkeita kertaluonteisia suunnittelukustannuksia (NRE) ja ilman joustamatonta arkkitehtuuria käyttävän prosessorin aiheuttamia sovelluskohtaisia rajoituksia. Kuten kohdassa Välitavoite – digitaalinen signaalinkäsittely mikrokontrollerilla kuvattiin, heidän kehitystyönsä alkaa siitä, että sovellusprosessori suorittaa suurimman osan laskentaintensiivisistä algoritmeista. He tunnistavat tästä lähtökohdasta käsin ne ohjelmiston tärkeimmät osat, jotka kuluttavat suurimman osan keskusyksikön (CPU) kellojaksoista, ja siirtävät nämä osiot HDL-toteutukseen. Graafinen esitys on hyvin samankaltainen kuin tähän mennessä esitelty, mutta sovellusohjelma on kuitenkin esitetty omana itsenäisenä lohkonaan, koska se voidaan toteuttaa joko isännässä (prosessorissa) tai FPGA-pohjaisessa laitteistossa.

Kuva 4: Sovellusohjelma, isäntäprosessori ja porttimatriisipohjainen laitteisto – käytetään satelliittiviestinnän esimerkissä.

Kuva 4: Sovellusohjelma, isäntäprosessori ja porttimatriisipohjainen laitteisto – käytetään satelliittiviestinnän esimerkissä.

Oheislaitteen suorituskyky paranee huomattavasti käyttämällä PCI (Peripheral Component Interconnect) -liitäntää ja isäntäprosessorin DMA (Direct Memory Access) -toimintoa. Tämä voidaan havaita parhaiten derandomisointiprosessin parannuksista. Kun tämä prosessi suoritettiin isäntäprosessorin ohjelmistolla, järjestelmän reaaliaikaisessa vasteessa oli selvästi pullonkaula. Kun prosessi kuitenkin siirrettiin ohjelmoitavaan porttimatriisiin, havaittiin seuraavat edut:

- Derandomisointiprosessi suoritettiin reaaliajassa aiheuttamatta pullonkauloja.

- Isäntäprosessorin laskennallinen kuormitus väheni merkittävästi ja se pystyi nyt hoitamaan paremmin siltä odotetun lokitehtävän.

- Koko järjestelmän kokonaissuorituskyky skaalautui ylöspäin.

Kaikki tämä saavutettiin ilman ASIC-piireihin liittyviä kustannuksia ja hyödyntäen samalla ohjelmoitavan logiikan joustavuutta [5]. Satelliittiviestintään liittyy huomattavia haasteita. Tällä lähestymistavalla nämä vaatimukset voidaan täyttää todistettavasti ja säilyttää joustavuus suunnittelussa.

Autoteollisuus – infotainment-esimerkki

Autojen viihdejärjestelmät kuuluvat vaativien kuluttajien erityispiirteisiin. Toisin kuin suurin osa autojen elektroniikasta, nämä laitteet ovat hyvin näkyviä ja niiden odotetaan tarjoavan poikkeuksellinen vasteaika ja suorituskyky. Suunnittelijat jäävät kuitenkin usein ahtaalle nykyisten suunnittelutarpeiden ja tulevaisuuden ominaisuuksien vaatiman joustavuuden väliin. Tässä esimerkissä käytetään signaalinkäsittelyn ja langattoman viestinnän toteutustarpeita rinnakkaisprosessoria käyttävän laitteistoarkkitehtuurin vahvuuksien esittelemiseen.

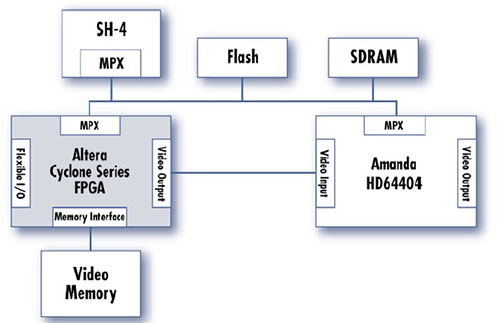

Yhden autojen viihdejärjestelmien vallitsevista arkkitehtuureista on julkaissut Delphi Delco Electronics Systems -yhtiö. Tässä arkkitehtuurissa käytettiin SH-4-mikrokontrolleria ja sen rinnalla oheislaitteena Hitachin HD64404 Amanda -ASIC-piiriä. Tämä arkkitehtuuri tyydytti yli 75 prosenttia automarkkinoiden perusviihdetoiminnoista, mutta se ei kuitenkaan pystynyt käsittelemään videoprosessointisovelluksia ja langatonta viestintää. Tähän nykyiseen suunnitelmaan voidaan lisätä joustavuutta ja ominaisuuksia lisäämällä arkkitehtuuriin ohjelmoitava porttimatriisi.

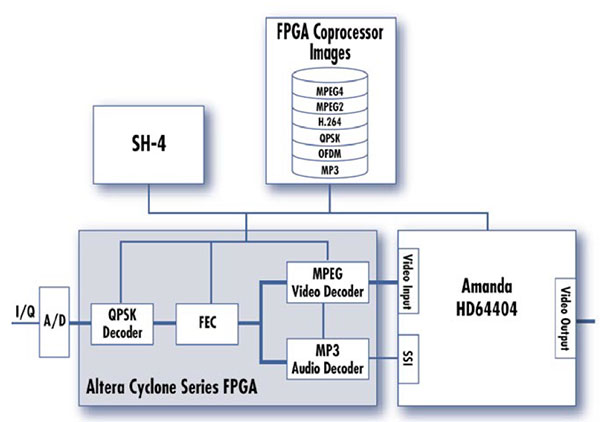

Kuva 5: Esimerkki 2 FPGA -rinnakkaisprosessoriarkkitehtuurista infotainment-sovelluksessa.

Kuva 5: Esimerkki 2 FPGA -rinnakkaisprosessoriarkkitehtuurista infotainment-sovelluksessa.

Kuvassa 5 esitetty arkkitehtuuri soveltuu sekä videoprosessointiin että langattoman viestinnän hallintaan. Kun DSP-toiminnot siirretään ohjelmoitavaan porttimatriisiin, Amanda-prosessori voi toimia järjestelmänhallinnan roolissa ja on vapaa langattoman tietoliikennepinon toteutusta varten. Koska sekä Amanda että ohjelmoitava porttimatriisi voivat käyttää ulkoista muistia, tietoja voidaan vaihtaa nopeasti järjestelmän prosessorien ja komponenttien välillä.

Kuva 6: Esimerkki 2 FPGA -rinnakkaisprosessoriarkkitehtuurista infotainment-sovelluksessa.

Kuva 6: Esimerkki 2 FPGA -rinnakkaisprosessoriarkkitehtuurista infotainment-sovelluksessa.

Kuvan 6 toisessa infotainment-kaaviossa havainnollistetaan ohjelmoitavan porttimatriisin kykyä käsitellä sekä saapuvaa nopeaa analogista dataa että videosovelluksissa tarvittavaa pakkausta ja koodausta. Itse asiassa kaikki nämä toiminnot voidaan siirtää ohjelmoitavaan porttimatriisiin ja niitä voidaan käsitellä rinnakkaisen prosessoinnin avulla reaaliaikaisesti.

Sisällyttämällä ohjelmoitava porttimatriisi olemassa olevaan laitteistoarkkitehtuuriin voidaan olemassa olevan laitteiston luotettava suorituskyky yhdistää joustavuuteen ja tulevaisuuden vaatimusten täyttämiseen. Rinnakkaisprosessoriarkkitehtuuri tarjoaa jopa olemassa olevissa järjestelmissä suunnittelijoille vaihtoehtoja, joita ei muuten olisi saatavilla [6].

Nopean prototyyppikehityksen edut

Prototyyppien nopea kehitysprosessi pyrkii pohjimmiltaan kattamaan huomattavan osan tuotekehitysalueesta tehtävien rinnakkaisella suorittamisella, ”vikojen” ja suunnitteluongelmien nopealla tunnistuksella sekä data- ja signaalipolkujen validoinnilla, erityisesti projektin kriittisellä polulla. Vaadittavilta projektialueilta tarvitaan kuitenkin riittävästi asiantuntemusta, jotta tämä prosessi voisi varmasti tuottaa suoritukseltaan virtaviivaistettuja ja tehokkaita tuloksia.

Perinteisesti tämä tarkoittaa, että tarvitaan laitteistosuunnittelija, sulautetun ohjelmiston suunnittelija tai DSP-suunnittelija ja HDL-suunnittelija. On olemassa paljon monen alan ammattilaisia, jotka voivat ehkä täyttää useita tehtäviä, mutta näiden toimien koordinointiin liittyy silti huomattava kuormitus.

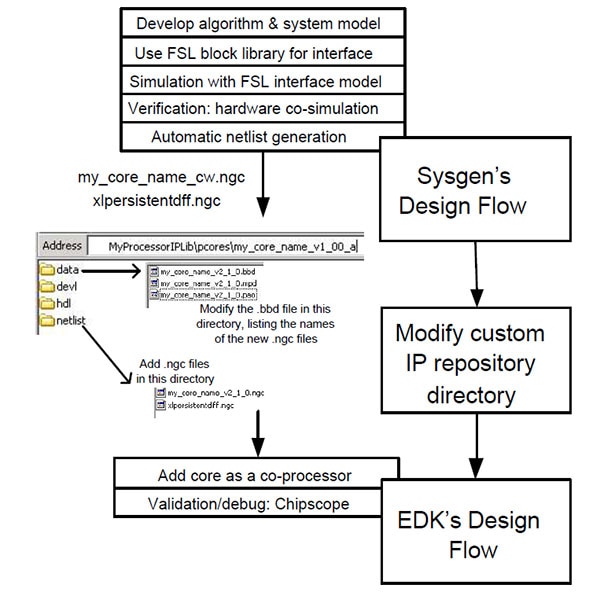

Kirjoittajat esittävät artikkelissaan An FPGA based rapid prototyping platform for wavelet coprocessors (FPGA-pohjainen nopea prototyyppien kehitysalusta wavelet-rinnakkaisprosessoreille), että rinnakkaisprosessoriarkkitehtuurin avulla yksi ainut DSP-insinööri voisi täyttää kaikki nämä roolit tehokkaasti ja toimivasti. Tiimi aloitti tätä tutkimusta varten halutun DSP-toiminnon suunnittelun ja simuloinnin MATLAB Simulink -työkalulla. Tällä oli kaksi päätehtävää: 1) halutun suorituskyvyn varmistaminen simuloinnin avulla ja 2) toiminta perustasona, johon tulevaisuuden suunnitteluvalintoja voitaisiin verrata ja jota voitaisiin käyttää referenssinä.

Simuloinnin jälkeen kriittiset toiminnot tunnistettiin ja jaettiin eri ytimiin. Nämä ovat softcore-komponentteja ja -prosessoreita, jotka voidaan syntetisoida ohjelmoitavassa porttimatriisissa. Tärkein vaihe tässä työssä oli määritellä näiden ytimien ja komponenttien välinen rajapinta ja verrata tiedonvaihdon suorituskykyä haluttuun, simuloituun suorituskykyyn. Tämä suunnitteluprosessi vastasi läheisesti Xilinxin sulautettujen järjestelmien suunnitteluvaiheita. Siitä esitetään yhteenveto alla olevassa kuvassa 7.

Kuva 7: Toteutuksen suunnitteluvaiheet.

Kuva 7: Toteutuksen suunnitteluvaiheet.

Jakamalla järjestelmä syntetisoitaviin ytimiin DSP-suunnittelija voi keskittyä signaalinkäsittelyketjun kriittisimpiin aspekteihin. Hänen ei tarvitse olla laitteisto- tai HDL-asiantuntija erilaisten softcore-prosessoreiden tai -komponenttien muokkaamiseksi, reitittämiseksi tai toteuttamiseksi ohjelmoitavassa porttimatriisissa. Riittää, että suunnittelija tuntee rajapinnan ja dataformaatit, niin hän voi kontrolloida täysin signaalipolkuja ja parantaa järjestelmän suorituskykyä.

Empiiriset havainnot – tapaustutkimus diskreetistä kosinimuunnoksesta

Empiiriset havainnot eivät ainoastaan vahvistaneet rinnakkaisprosessoriarkkitehtuurin tarjoamaa joustavuutta sulautettujen järjestelmien suunnittelussa, vaan ne myös osoittivat nykyaikaisten porttimatriisityökalujen tarjoamat mahdollisuudet suorituskyvyn parantamiseen. Jäljempänä mainittujen kaltaisia parannuksia ei välttämättä ole saatavilla tai niiden vaikutus voi olla vähäisempi muissa laitteistoarkkitehtuureissa. Laskentaintensiiviseksi algoritmiksi valittiin diskreetti kosinimuunnos (DCT) ja näiden havaintojen keskipisteessä oli sen muunnos C-pohjaisesta toteutuksesta HDL-pohjaiseen toteutukseen. DCT valittiin, koska tätä algoritmia käytetään digitaalisessa signaalinkäsittelyssä hahmontunnistukseen ja suodatukseen [8]. Empiiriset havainnot perustuivat laboratoriotöihin, joita kirjoittaja ja tämän työtoverit suorittivat saadakseen Xilinx Alliance Partnerin sertifioinnin vuosille 2020–2021.

Tässä työssä käytettiin seuraavia välineitä ja laitteita:

- Vivado HLS v2019

- Arvioinnissa ja simuloinnissa käytetty laite oli xczu7ev-ffvc1156-2-e.

Ensiksikin C-pohjainen toteutus DCT-algoritmi käyttää kahta 16-bittisten lukujen taulukkoa; taulukko ”a” on DCT:n tulotaulukko ja taulukko ”b” on DCT:n lähtötaulukko. Dataleveydeksi (DW) määritellään siten 16 ja elementtien lukumäärä taulukoissa (N) on 1024/DW eli 64. Lopuksi DCT-matriisin koko (DCT_SIZE) asetetaan arvoon 8, mikä tarkoittaa, että käytettävä matriisi on kooltaan 8 x 8.

Tässä artikkelissa lähtöoletuksena on se, että suunnittelija voi kehittää ja validoida algoritmin toiminnallisuuden nopeasti C-pohjaisen algoritmitoteutuksen avulla. Vaikka suoritusaika on tärkeä tekijä, tämä validointi antaa toiminnallisuudelle suuremman painoarvon kuin suoritusajalle. Tämä painotus on mahdollista, koska tämän algoritmin lopullinen toteutus tehdään ohjelmoitavassa porttimatriisissa, missä laitteistokiihdytys, silmukoiden purkaminen ja muut tekniikat ovat helposti käytettävissä.

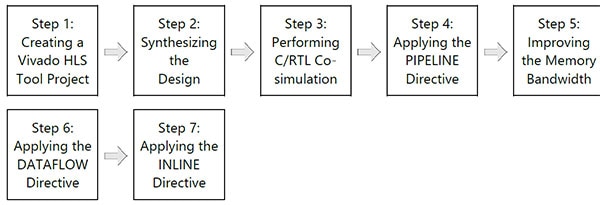

Kuva 8: Xilinx Vivado HLS -suunnitteluvaiheet

Kuva 8: Xilinx Vivado HLS -suunnitteluvaiheet

Kun DCT-koodi on luotu Vivado HLS -työkalussa projektina, seuraavassa vaiheessa voidaan aloittaa ratkaisun syntetisointi ohjelmoitavassa porttimatriisissa toteutusta varten. Juuri tässä seuraavassa vaiheessa käy ilmi joitakin merkittävimmistä eduista, joita algoritmin suorittamisen siirtäminen mikrokontrollerista ohjelmoitavaan porttimatriisiin tuo mukanaan. Tämä vaihe vastaa edellä käsiteltyä välitavoitetta järjestelmänhallinta mikrokontrollerilla.

Nykyaikaiset FPGA-työkalut tarjoavat runsaasti optimointi- ja parannusmahdollisuuksia, jotka lisäävät huomattavasti monimutkaisten algoritmien suorituskykyä. Ennen tulosten analysointia on syytä pitää mielessä joitakin tärkeitä termejä:

- Latenssi – silmukan kaikkien iteraatioiden suorittamiseen tarvittavien kellojaksojen määrä [10]

- Aikaväli – kellojaksojen määrä ennen kuin silmukan seuraava iteraatio alkaa käsitellä dataa [11]

- BRAM – Block Random Access Memory, lohkoihin perustuva hajasaantimuisti

- DSP48E – UltraScale-arkkitehtuurin digitaalisen signaalinkäsittelyn siivu

- FF – Flipflop, kiikku

- LUT – hakutaulukko

- URAM – Unified Random-Access Memory, yhtenäistetty hajasaantimuisti (voi koostua yksittäisestä transistorista)

|

||||||||||||||||||||||||||||||||||||||||

Taulukko 1: FPGA-algoritmin suorittamisen optimoinnin tulokset (latenssi ja aikaväli).

|

Taulukko 2: Ohjelmoitavan porttimatriisialgoritmin suorittamisen optimoinnin tulokset (resurssien käyttö).

Oletusarvoinen optimointi

Optimoinnin oletusasetus saadaan tuloksesta, jossa C-pohjainen algoritmi käännetään sellaisenaan muuttamatta syntetisoitavalle HDL-kielelle. Mitään optimointeja ei ole aktivoitu, ja tätä voidaan käyttää suorituskykyreferenssinä muiden optimointien parempaan ymmärtämiseen.

Liukuhihnoita sisäinen silmukka

PIPELINE (liukuhihna) -direktiivi ohjaa Vivado HLS -sovellusta purkamaan sisäiset silmukat, jotta uuden datan käsittely voidaan aloittaa vaikka edellinen data on vielä liukuhihnalla. Näin uuden datan ei tarvitse odottaa, että olemassa oleva data on valmis, ennen kuin käsittely voi alkaa.

Liukuhihnoita ulkoinen silmukka

Kun PIPELINE (liukuhihna) -direktiiviä sovelletaan ulkoiseen silmukkaan, ulkoisen silmukan toiminnot liukuhihnoitetaan. Sisäisten silmukoiden toiminnot tapahtuvat nyt kuitenkin samanaikaisesti. Sekä latenssi että aikaväli puolittuvat soveltamalla tätä suoraan ulkoiseen silmukkaan.

Taulukon osiointi

Tämä direktiivi kuvaa silmukoiden sisällön taulukkoihin ja tasoittaa siten kaiken muistin käytön yksittäisiin elementteihin näissä taulukoissa. Tämän seurauksena RAM-muistia kuluu enemmän, mutta myös tämän algoritmin suoritusaika puolittuu.

Tietovuo

Tämän direktiivin avulla suunnittelija voi määritellä kellojaksojen tavoitemäärän yksittäisten syötteiden lukemisen välillä. Tätä direktiiviä tuetaan vain ylätason funktiossa. Ainoastaan tällä tasolla olevat silmukat ja funktiot hyötyvät tästä direktiivistä.

Inline

INLINE-direktiivi tasoittaa kaikki silmukat, sekä sisäiset että ulkoiset. Nyt sekä rivi- että sarakeprosesseja voidaan suorittaa samanaikaisesti. Tarvittavien kellojaksojen määrä pidetään minimissä, vaikka se kuluttaakin enemmän FPGA-resursseja.

Yhteenveto

Rinnakkaisprosessoria käyttävä laitteistoarkkitehtuuri tarjoaa sulautetun järjestelmän suunnittelijalle huipputehokkaan alustan, joka mahdollistaa joustavuuden suunnittelussa koko tuotekehityksen ajan ja myös tuotteen markkinoilletuonnin jälkeen. Kun algoritmit validoidaan ensin C- tai C++-kielellä, prosessit, data- ja signaalipolut sekä kriittiset toiminnot voidaan todentaa suhteellisen lyhyessä ajassa. Kun prosessori-intensiiviset algoritmit sitten käännetään FPGA-rinnakkaisprosessorille, suunnittelija voi hyödyntää laitteistokiihdytyksen ja modulaarisemman suunnittelun etuja.

Jos osia vanhenee tai tarvitaan optimointia, sama arkkitehtuuri mahdollistaa nämä muutokset. Ratkaisuun voidaan lisätä uusia mikrokontrollereita ja uusia ohjelmoitavia porttimatriiseja samalla kun rajapinnat voidaan pitää suhteellisen muuttumattomina. Koska sekä mikrokontrolleri että ohjelmoitava porttimatriisi voidaan lisäksi päivittää jälkikäteen, käyttäjäkohtaisia muutoksia ja optimointeja voidaan tehdä jälkikäteen ja etänä.

Lopuksi voidaan todeta, että tässä arkkitehtuurissa yhdistyvät mikrokontrollerin kehitysnopeus ja käytettävyys sekä ohjelmoitavan porttimatriisin suorituskyky ja laajennettavuus. Koska optimoinnit ja suorituskyvyn parannukset ovat mahdollisia kaikissa kehitysvaiheissa, rinnakkaisprosessoriarkkitehtuuri voi täyttää kaikkein haastavimmatkin vaatimukset – sekä nykyisissä että tulevissa ratkaisuissa.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.